# SinOne SC95F8767/8766/8765/8763/8762

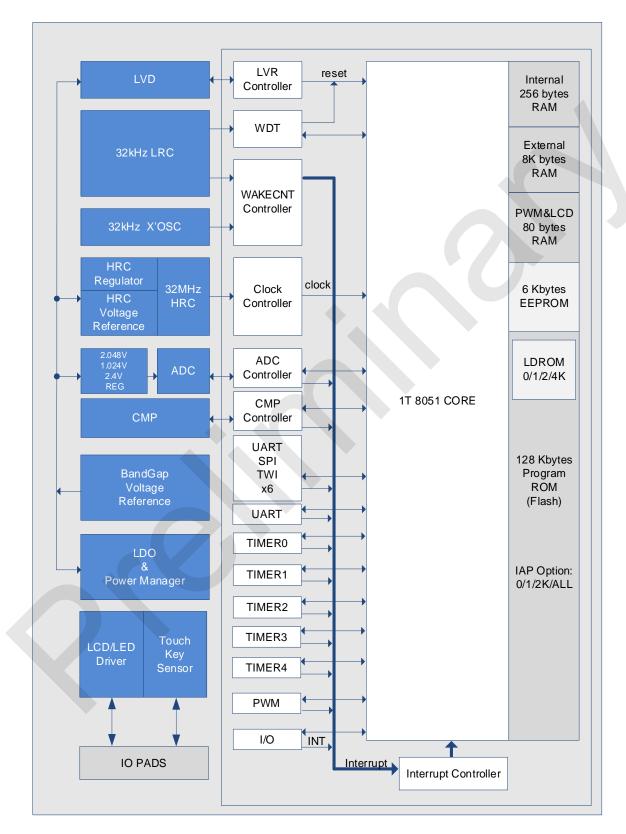

Super High-speed 1T 8051 Core Flash MCU, 8 Kbytes SRAM, 128 Kbytes Flash, 0~4 Kbytes LDROM, 6 Kbytes Independent LDROM, 31-channel high sensitivity TouchKey circuits ,12-bit ADC, 14-channel 16-bit PWM, 5 Timers, MDU, UART, 6-channel USCI, CRC Check Module, 1 Analog Comparator

## **1** General Description

SC95F8767/8766/8765/8763/8762 (hereinafter referred to as the SC95F876X) is a series of enhanced 1T 8051 core industry-standard Flash Microcontroller unit (MCU) with integrated TouchKey function, the instruction set is compatible with the standard 8051 series.

The SC95F876X has a Super-high-speed 1T 8051 CPU core with an operating frequency of up to 32 MHz.

The SC95F876X integrates a hardware multiplier and divider hardware CRC and dual DPTR data pointers to accelerate data operations and movement speed. The hardware multiplier and divider and hardware CRC does not occupy CPU cycles, and the operation is implemented by hardware, and the speed is faster than the multiplication and division speed realized by software; dual DPTR data pointers can be used to accelerate data storage and movement.

The SC95F876X has high performance and reliability, with a wide operating voltage of 2.0V~5.5V, a super-wide operating temperature of -40°C to 105°C, and has good ESD performance and EFT anti-interference ability. Using the industry-leading eFlash process, the Flash can be written more than 100,000 times, and can be stored for 100 years at room temperature.

The SC95F876X has a built-in low power consumption WDT Watchdog Timer. It has a 4-level selectable voltage LVR low voltage reset function and a system clock monitoring function. It has low power consumption capability in operation and power-down modes. Under normal operating mode: about 6mA@32M at 5V.

The SC95F876X series is also integrated with super rich hardware resources: built-in 31-channel (high sensitivity) touchkey circuits, 128 KbytesFlash ROM, SRAM: internal 256 bytes+ external 8 Kbytes+ PWM&LCD 80 bytes,

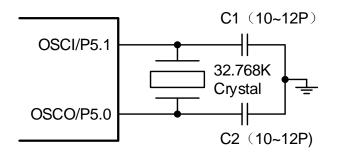

6 Kbytes EEPROM, up to 46 GP I/O (partially gradable control), 16 IO can be externally interrupted, 5 16-bit timers, 14-channel 16-bit PWM:8-channel multi-function dead zone complementary PWM,6 channel PWM output of timer,1 UART,6 USCI(UART/SPI/IIC), Built-in LCD/LED hardware driver, internal ±2% high-precision high-frequency 32/16/8/4 MHz oscillator and ±4% precision low-frequency 32 kHz oscillator, external 32.768 kHz resources such as crystal oscillators. 1 analog comparator, 17 channels 12-bit high precision ADC.

The SC95F876X is very convenient for development and debugging, with ISP (In-System Programming), ICP (In-Circuit Programming) and IAP (In-Application Programming). Allow the chip to debug and upgrade the program memory directly on the circuit board when the chip is online or powered.

The SC95F876X has very excellent anti-jamming performance and excellent touchkey performance. It is very suitable for various applications about touchkey and main contral system, such as Intelligent home appliances and Intelligent House System, Internet of things, wireless communication, game consoles and other industrial controls, and Consumer application areas.

## 2 Features

#### **Operating Conditions**

- Voltage Range: 2.0V~5.5V

- Temperature Range: -40°C ~ +105°C

#### EMS

- ESD

- HBM: MIL-STD-883J Class 3A

- MM: JEDEC EIA/JESD22-A115 Class C

- CDM: ANSI/ESDA/JEDEC JS-002-2018 Class C3

#### • EFT

■ EN61000-4-4 Level 4

#### Package

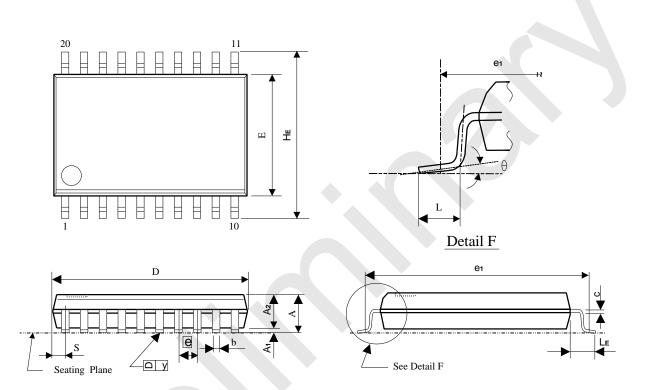

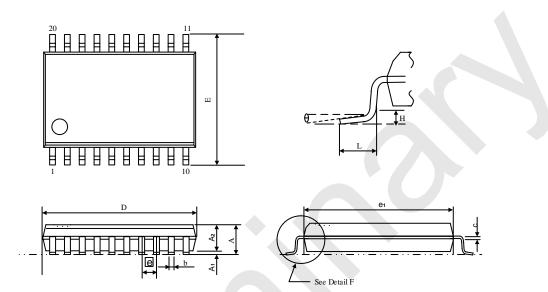

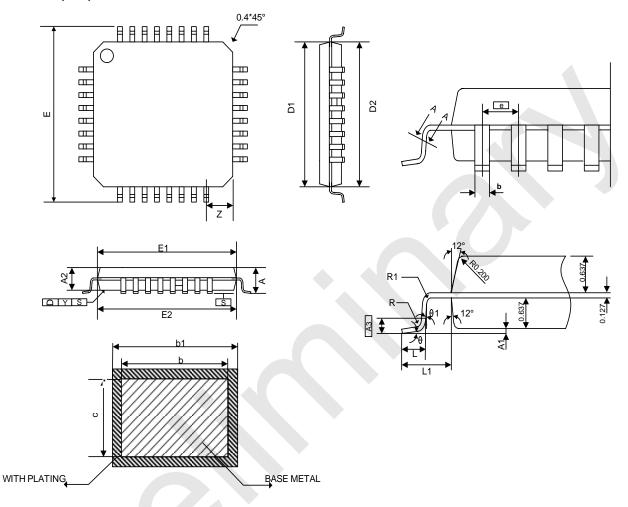

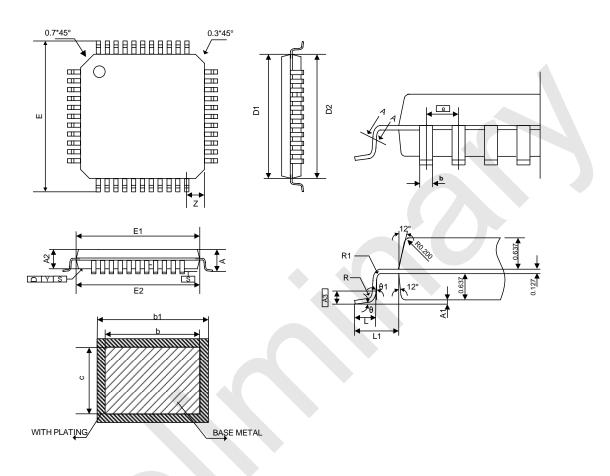

- 20 PIN: SOP20 / TSSOP20

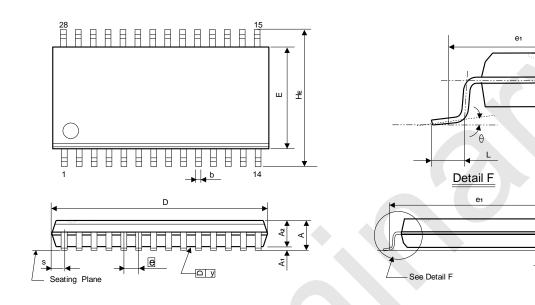

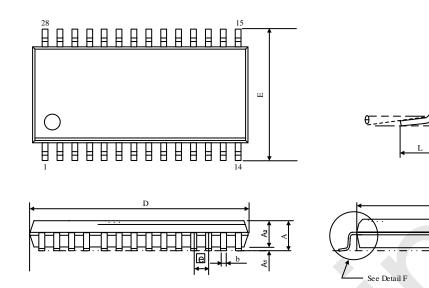

- 28 PIN: SOP28 / TSSOP28

- 32 PIN: LQFP32 (7X7) / QFN32 (5X5)

- 44 PIN: LQFP44 (10X10)

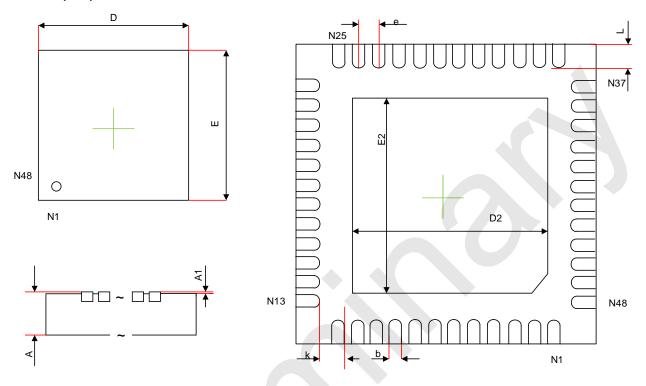

- 48 PIN: LQFP48 (7X7) / QFN48 (7X7)

#### CPU

- Super-high-speed 1T 8051 core

- The instruction set compatible with 8051

- The execution speed is about twice that of other 1T 8051

- Double data pointers (DPTRs)

#### Flash ROM

- 128 Kbytes Flash ROM

- MOVC disables addressing 0000H ~ 00FFH

- Can be rewritten 100,000 times

- APROM area allowed IAP operation in Flash can be set to 0K/1K/2K/All APROM by Code Option.

#### LDROM

- BootLoader code memory

- LDROM area can be set to 0K/1K/2K/4K by Code Option

#### EEPROM

- Independent 6 Kbytes EEPROM

- Can be rewritten 100,000 times, has more than 100-year preservation life in the ambient temperature of 25°C

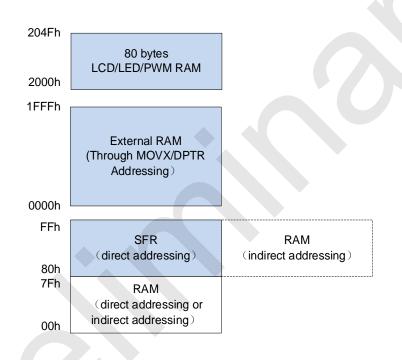

#### SRAM

- 256 bytes on-chip direct access RAM

- 8 Kbytes on-chip Indirect access RAM

- 80 bytes PWM&LCD RAM

#### Flash Programming and Emulation

• 2-wire JTAG programming and emulation interface

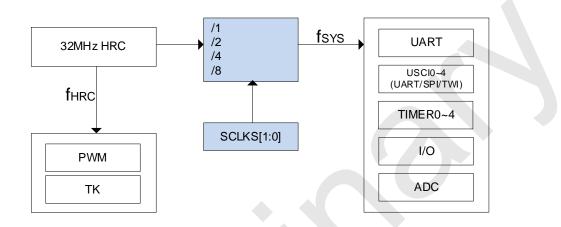

#### System clock (f<sub>sys</sub>)

- Built-in high frequency 32 MHz oscillator (f<sub>HRC</sub>)

- can be selected and set by the programmer as: 32/16/8/4 MHz@2.0~5.5V

- Frequency Error: Within ±1% @ -40 ~ 85°C @ 2.0 ~ 5.5V

- Frequency Error: Within ±2% @ -40 ~ 105°C @ 2.0 ~ 5.5V

- The system clock can be automatically calibrated by 32.768 kHz external crystal oscillator, after calibration HRC accuracy can be infinitely close to the accuracy of external 32.768 kHz crystal oscillator.

#### Built-in low-frequency crystal oscillator circuit:

• 32.768k oscillator can be connected externally as a Base Timer clock source.

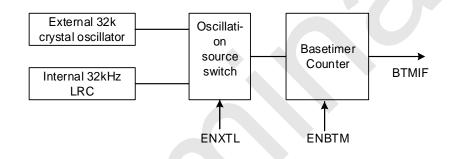

#### Built-in low-frequency 32 kHz oscillator (LRC):

- used as the clock source for Base Timer and WDT and wake up STOP

- Frequency Error: After the register correction, within ±4% @ -20 ~ 85°C @ 4.0 ~ 5.5V

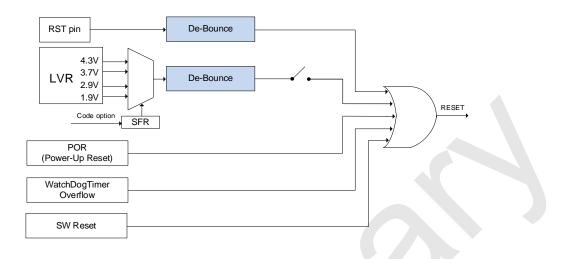

#### Low-voltage Reset (LVR)

- 4 options of reset voltage: 4.3/3.7/ 2.9/1.9V,

- the default value can be selected by the Code Option

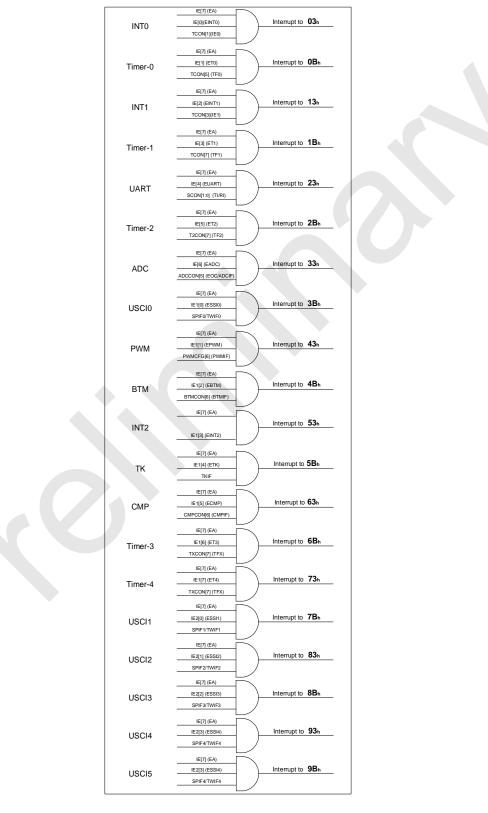

#### Interrupts (INT)

- Timer 0~Timer 4, INT0~2, ADC, PWM, UART, USCI0~5, Base Timer, TK, CMP 20 interrupt sources

- External interrupt contains 3 interrupt vectors, 16 interrupt ports. All can set up rising edge, falling edge, dual edge interrupt.

- Two-level interrupt priority capability

#### **Digital Peripheral**

- GPIO: Up to 46 bidirectional independently controllable I/O ports

- Independent setting of pull-up resistors

- P0~P3L(P3.0/1/2/3) port source drive capacity is controlled by four levels

- All IO ports have large sink current drive capability (50mA)

- Built-in WDT, optional clock frequency division ratio

- 5 Timers: Timer0~4、Timer1、Time2、Timer3 and Timer4

- Time2、Timer3 and Timer4 have Capture function

- Time2、Timer3 and Timer4 each can provide two conventional PWM

- 6-channel 16-bit conventional PWM

- Time2、Timer3 and Timer4 each can provide two conventional PWM

- 8-channel 16-bit multi-function PWM

- Public cycle and the duty cycle can be set separately

- Complementary PWM waveforms with dead zones can be output

- One independent UART communication port UART0

- Six UART/SPI/TWI communication interfaces (USCI)

- When USCI0 is set to SPI0, the driving capability of the pins corresponding to its signal port will be enhanced

- Built-in CRC check module

- Integrated with 16 \* 16-bit hardware Multiplier-Divide Unit (MDU)

#### LCD/LED driver

- Choose one of two LCD/LED, share registers and IO ports

- 8 X 24, 6 X 26, 5 X 27, or 4X 28 segments LED driver

- LED segment port source drive capability is selectable in four levels

- 8 X 24, 6 X 26, 5 X 27, or 4 X 28 segments LCD driver

Page 4 of 260

#### **Analog Peripheral**

- 31-channel high sensitivity TouchKey circuit.

- Applicable to TouchKey sensor, proximity induction and other TouchKey applications featuring high requirements on sensitivity

- Have very strong anti-interference ability which is able to pass 10V dynamic CS test

- Support self-capacitanceand reciprocal- capacitance mode.

- Support low power consumption mode.

- Complete development support: High-flexible touch software library, intelligent software of debugging.

- 17-channel 12-bit±2LSB ADC

- Build-in reference voltage of 2.048V, 1.024V and 2.4V

- The ADC reference voltages is optional: VDD, internal 2.048V, internal 1.024V and 2.4V

- 1 internal channel can measure the voltage of the power supply

- ADC conversion complete interruption can be set

- 1 Analog Comparator

- 4-channel input and 1-channel reference voltage input

- 16-level optional comparison voltage

#### **Power Saving Mode**

- IDLE Mode: can be woken up by any interrupt

- STOP Mode: can be woken up by INT0~2, Base Timer TK and CMP.

## Naming Rules for 95 Series Products

| Name | SC | 95 | F | 8 | 7 | 6 | 7 | х | Р | 48 | R   |

|------|----|----|---|---|---|---|---|---|---|----|-----|

| S/R  | 1  | 2  | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11) |

| S/R | Meaning                                                                                           |

|-----|---------------------------------------------------------------------------------------------------|

| 1   | SinOne Chip abbreviation                                                                          |

| 2   | Name of product series                                                                            |

| 3   | Product Type (F: Flash MCU)                                                                       |

| 4   | Serial Number: 7: GP Series, 8: TK series                                                         |

| 5   | ROM Size: 1 for 2K, 2 for 4K, 3 for 8K, 4 for 16K, 5 for 32K and 6 for 64K                        |

| 6   | Subseries Number.: 0 ~ 9, A ~ Z                                                                   |

| Ø   | Number of Pins: 0: 8pin, 1: 16pin,2: 20pin,3: 28pin,5: 32pin,6: 44pin,7: 48pin,8: 64pin,9: 100pin |

| 8   | Version:(default, B, C, D)                                                                        |

| 9   | Package Type: (D: DIP; M: SOP; X: TSSOP; F: QFP; P: LQFP; Q: QFN; K: SKDIP)                       |

| 10  | Number of Pins.                                                                                   |

| 11  | Packaging Mode: (U: Tube; R: Tray; T: Reel)                                                       |

## **Ordering Information**

| PRODUCT ID    | PACKAGE       | PACK |

|---------------|---------------|------|

| SC95F8762M20U | SOP20         | TUBE |

| SC95F8762X20U | TSSOP20       | TUBE |

| SC95F8763M28U | SOP28         | TUBE |

| SC95F8763X28U | TSSOP28       | TUBE |

| SC95F8765P32R | LQFP32(7X7)   | TRAY |

| SC95F8765Q32R | QFN32(5X5)    | TRAY |

| SC95F8766P44R | LQFP44(10X10) | TRAY |

| SC95F8767P48R | LQFP48(7X7)   | TRAY |

| SC95F8767Q48R | QFN48(7X7)    | TRAY |

## **Contents**

| 1 GENERAL DESCRIPTION                                                                                                                              | 1    |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2 FEATURES                                                                                                                                         | 2    |

| NAMING RULES FOR 95 SERIES PRODUCTS                                                                                                                | 6    |

| ORDERING INFORMATION                                                                                                                               | 7    |

| CONTENTS                                                                                                                                           | 8    |

| 3 PIN DESCRIPTION                                                                                                                                  |      |

| 3.1 Pin Configuration                                                                                                                              |      |

| 3.1.1 48/44 Pin Definition                                                                                                                         |      |

| 4 INNER BLOCK DIAGRAM                                                                                                                              |      |

| 5 FLASH ROM AND SRAM                                                                                                                               |      |

| 5.1 APROM and LDROM                                                                                                                                |      |

| 5.1.1 Flash ROM Sectors                                                                                                                            |      |

| 5.2 6K bytes independent EEPROM                                                                                                                    |      |

| 5.3 96 bits Unique ID Area                                                                                                                         |      |

| 5.3.1 Unique ID Read Operating Demo Program In C Language                                                                                          |      |

| 5.4 User ID Area                                                                                                                                   |      |

| 5.5 Programming                                                                                                                                    |      |

| 5.6 In Application Programming (IAP)                                                                                                               |      |

| 5.6.1 IAP Operation Related Register<br>5.6.2 IAP Operation process<br>5.6.3 IAP Operating Demo Program In C Language<br>5.6.4 IAP Operation notes |      |

| 5.7 BootLoader                                                                                                                                     |      |

| 5.7.1 BootLoader Mode operation related registers                                                                                                  | 41   |

| 5.8 Encryption                                                                                                                                     |      |

| 5.9 Code Option Area (User Programming Settings)                                                                                                   |      |

| 5.9.1 Customer-Option-related Registers Operation Instructions                                                                                     |      |

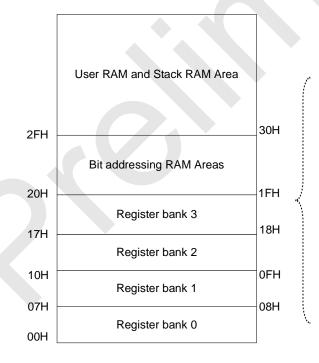

| 5.10 SRAM                                                                                                                                          | 53   |

| 5.10.1 Internal 256 Bytes SRAM                                                                                                                     |      |

| 5.10.2 External 8 Kbytes SRAM<br>5.10.3 External 80 bytes PWM&LCD/LED SRAM                                                                         |      |

| 6 SPECIAL FUNCTION REGISTER (SFR)                                                                                                                  |      |

| 6.1 SFR Mapping                                                                                                                                    |      |

| 6.2 SFR Instructions                                                                                                                               |      |

| 6.2.1 SFR                                                                                                                                          |      |

| <ul><li>6.2.2 PWM0 Duty Cycle Adjustment Register(R/W)</li><li>6.2.3 PWM2~4 Duty Cycle Adjustment Register(R/W)</li></ul>                          |      |

| 6.2.4 LCD/LED display RAM configuration (R/W)                                                                                                      |      |

| 6.2.5 Introduction of Common Special Function Registers of 8051 Co                                                                                 |      |

| Page 8 of 260                                                                                                                                      | V0.1 |

| Program Counter PC                                                                    |     |

|---------------------------------------------------------------------------------------|-----|

| Accumulator ACC (E0H)                                                                 | 67  |

| B Register (F0H)                                                                      |     |

| Stack Pointer SP (81H)                                                                |     |

| Data Pointers DPTR0 (82H, 83H), DPTR1 (84H, 85H) And Its Selection Register DPS (86H) |     |

| 7 POWER, RESET AND SYSTEM CLOCK                                                       |     |

| 7.1 Power Circuit                                                                     |     |

| 7.2 Power-on Reset                                                                    |     |

| 7.2.1 Reset Stage                                                                     |     |

| 7.2.2 Loading Information Stage<br>7.2.3 Normal Operation Stage                       |     |

| 7.3 Reset Modes                                                                       |     |

| 7.3.1 External Reset                                                                  |     |

| 7.3.2 Low-voltage Reset LVR                                                           |     |

| 7.3.3 Power-on Reset (POR)                                                            | 73  |

| 7.3.4 Watchdog Reset (WDT)                                                            |     |

| 7.3.5 Software Reset<br>7.3.6 Register Reset Value                                    |     |

| 7.4 High- frequency System Clock Circuit                                              |     |

| 7.5 Low- frequency RC Oscillator and Low- frequency Clock Timer                       |     |

| 7.6 Power Saving Modes                                                                |     |

| 8 CPU AND INSTRUCTION SET                                                             |     |

| 8.1 CPU                                                                               |     |

| 8.2 Addressing Mode                                                                   |     |

|                                                                                       |     |

| 8.2.1 Immediate Addressing                                                            |     |

| 8.2.3 Indirect Addressing                                                             |     |

| 8.2.4 Register Addressing                                                             |     |

| 8.2.5 Relative Addressing                                                             |     |

| 8.2.6 Indexed Addressing                                                              |     |

| 8.2.7 Bits Addressing 9 INTERRUPTS                                                    |     |

|                                                                                       |     |

| 9.1 Interrupt Source and Vector                                                       |     |

| 9.2 Interrupt Structure Diagram                                                       |     |

| 9.3 Interrupt Priority                                                                |     |

| 9.4 Interrupt Processing Flow                                                         |     |

| 9.5 Interrupt-related SFR Registers                                                   |     |

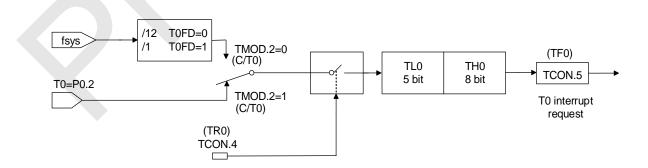

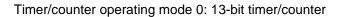

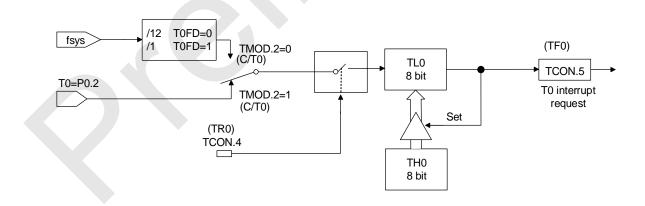

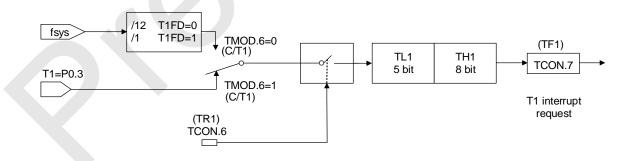

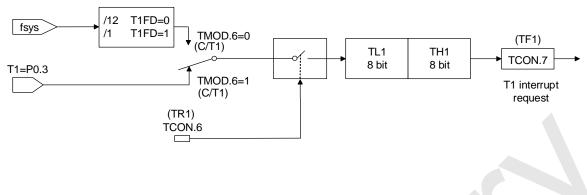

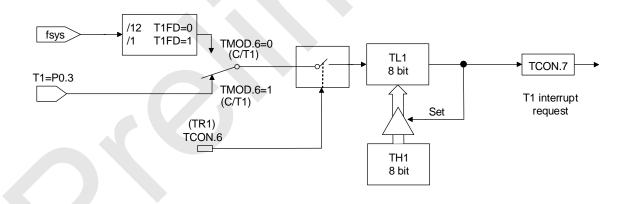

| 10 TIMER/COUNTER TO AND T1                                                            |     |

| 10.1 T0 and T1-related Registers                                                      |     |

| 10.2 T0 Operating Modes                                                               |     |

| 10.3 T1 Operating Mode                                                                |     |

| 11 TIMER/COUNTER T2/T3/T4                                                             | 113 |

| 11.1 T2/3/4-related Registers                                                         |     |

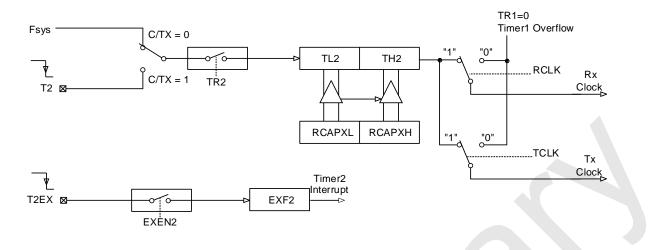

| 11.2 Timer 2                                                                                                                                                                                                                                | 114 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11.3 Timer 3                                                                                                                                                                                                                                | 118 |

| 11.4 Timer 4                                                                                                                                                                                                                                | 122 |

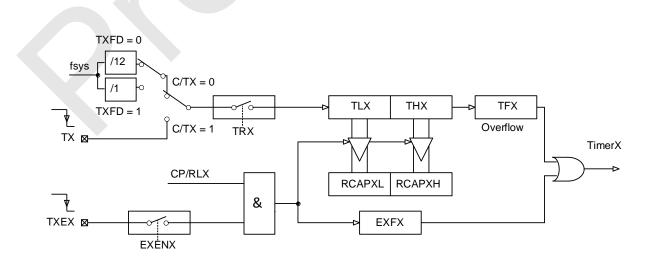

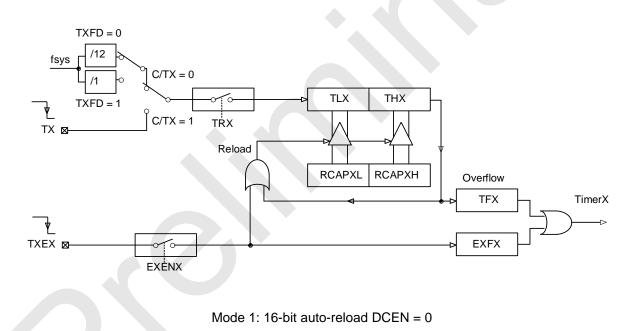

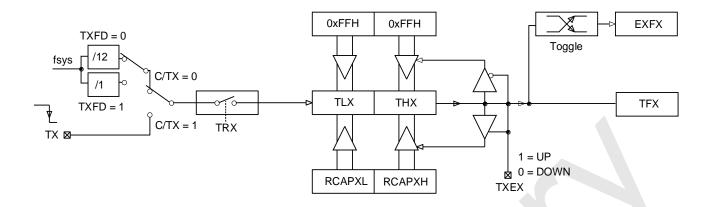

| 11.5 Timer 2/3/4 Operating Modes                                                                                                                                                                                                            | 125 |

| 11.5.1 Timer 2/3/4 Operating Modes                                                                                                                                                                                                          | 126 |

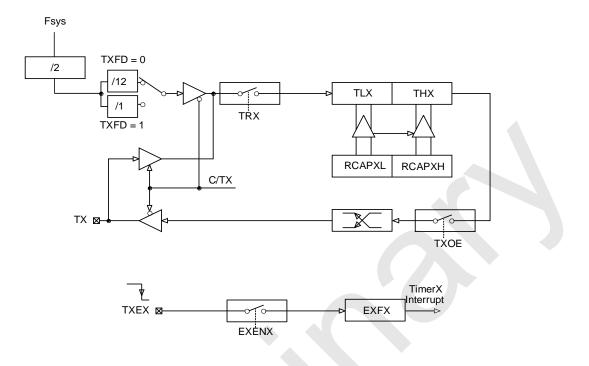

| 12 PWM2/3/4                                                                                                                                                                                                                                 |     |

| 12.1 PWM2/3/4 related Registers                                                                                                                                                                                                             |     |

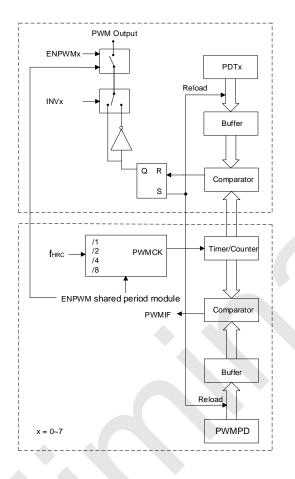

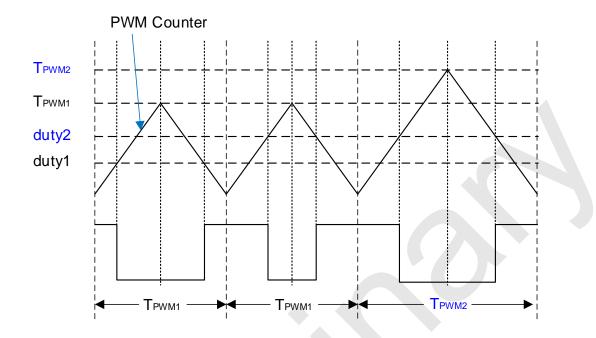

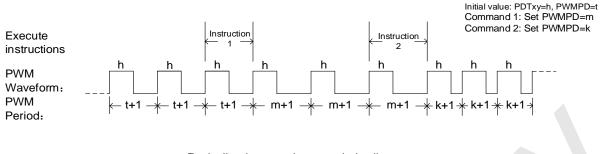

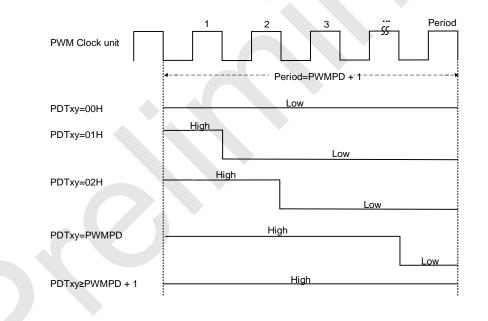

| 12.2 PWM2/3/4 Duty Variation Characteristics                                                                                                                                                                                                |     |

| 12.3 PWM2/3/4 Cycle Variation Characteristics                                                                                                                                                                                               |     |

| 13 PWM0                                                                                                                                                                                                                                     |     |

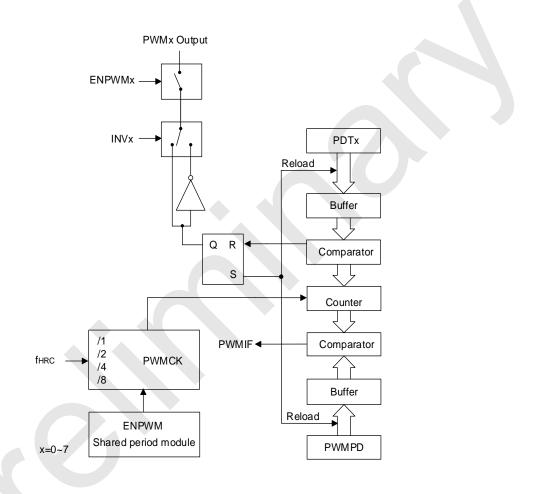

| 13.1 PWM Structure Diagram                                                                                                                                                                                                                  |     |

| 13.2 PWM0 General Configuration Register                                                                                                                                                                                                    |     |

| 13.2.1 PWM0 General Configuration Register                                                                                                                                                                                                  |     |

| 13.2.2 PWM0 Fault Detection Function Setting                                                                                                                                                                                                | 144 |

| 13.3 PWM0 Independent Mode                                                                                                                                                                                                                  |     |

| 13.3.1 PWM0 Independent Mode Block Diagram<br>13.3.2 PWM0 Independent Mode Duty Cycle Configuration                                                                                                                                         | 148 |

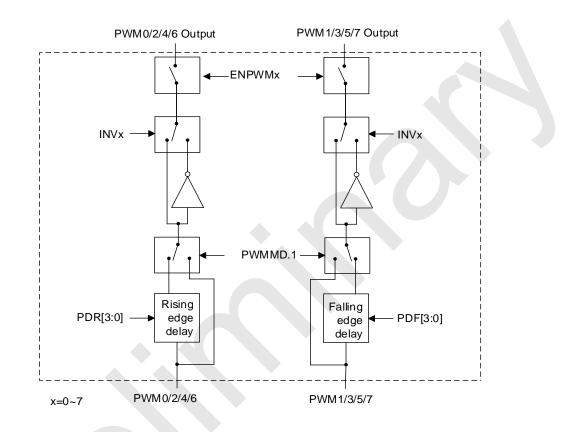

| 13.4 PWM0 Complementary Model                                                                                                                                                                                                               |     |

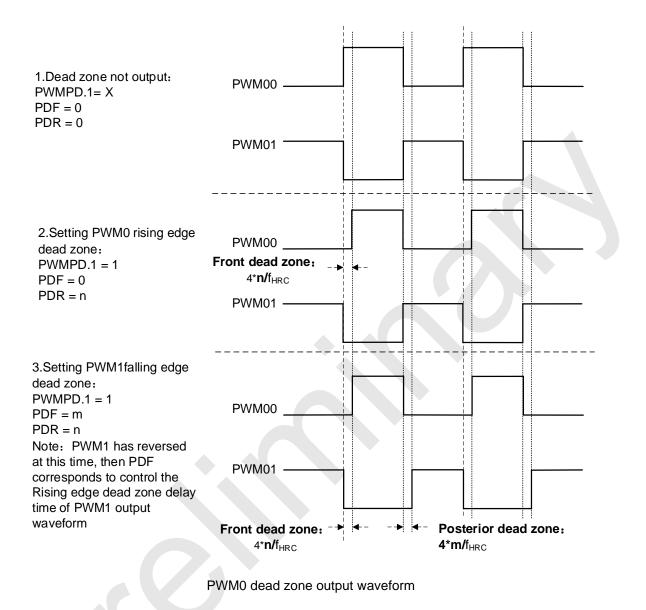

| <ul> <li>13.4.1 PWM0 Block Diagram of Complementary Mode</li> <li>13.4.2 PWM Complementary Mode Duty Cycle Configuration</li> <li>13.4.3 PWM Complementary Mode Dead Time Setting</li> <li>13.4.4 PWM0 Dead Zone Output Waveform</li> </ul> |     |

| 13.5 PWM0 Waveforms and Directions                                                                                                                                                                                                          |     |

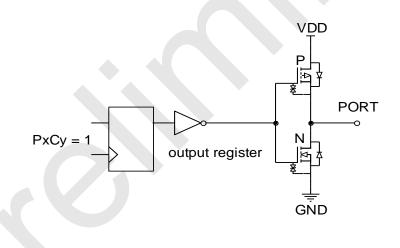

| 14 GENERAL-PURPOSE I/O (GPIO)                                                                                                                                                                                                               |     |

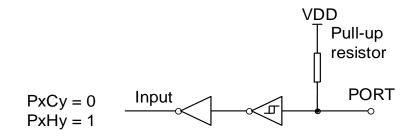

| 14.1 GPIO Structure Diagram                                                                                                                                                                                                                 |     |

| 14.2 I/O Port-related Registers                                                                                                                                                                                                             |     |

| 15 LCD/LED DISPLAY DRIVER                                                                                                                                                                                                                   |     |

| 15.1 LCD/LED Display Drive-related Registers                                                                                                                                                                                                |     |

| 15.2 LCD/LED Display RAM Configuration                                                                                                                                                                                                      |     |

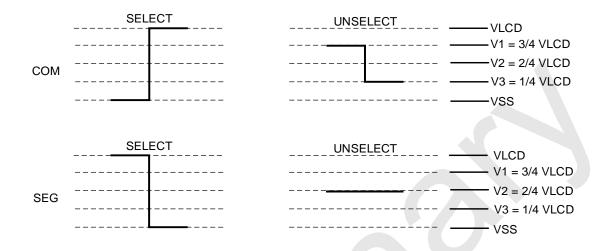

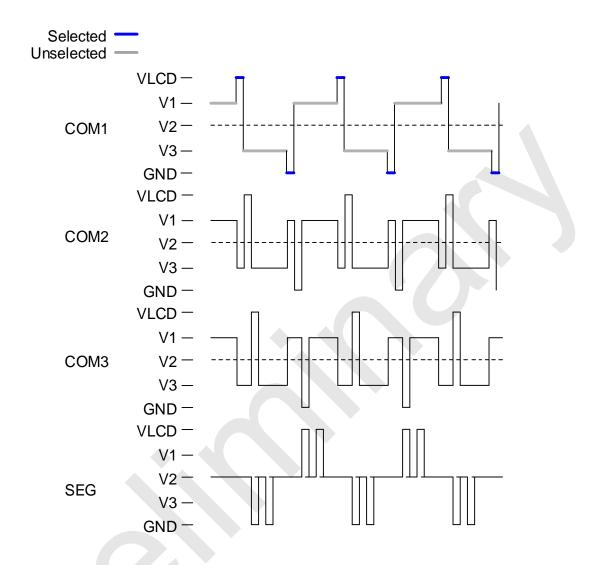

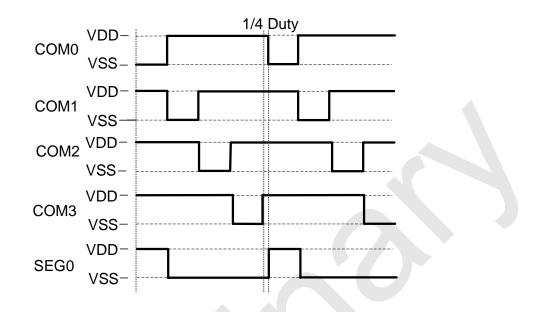

| 15.3 LCD Waveform                                                                                                                                                                                                                           |     |

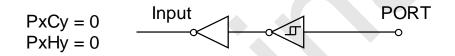

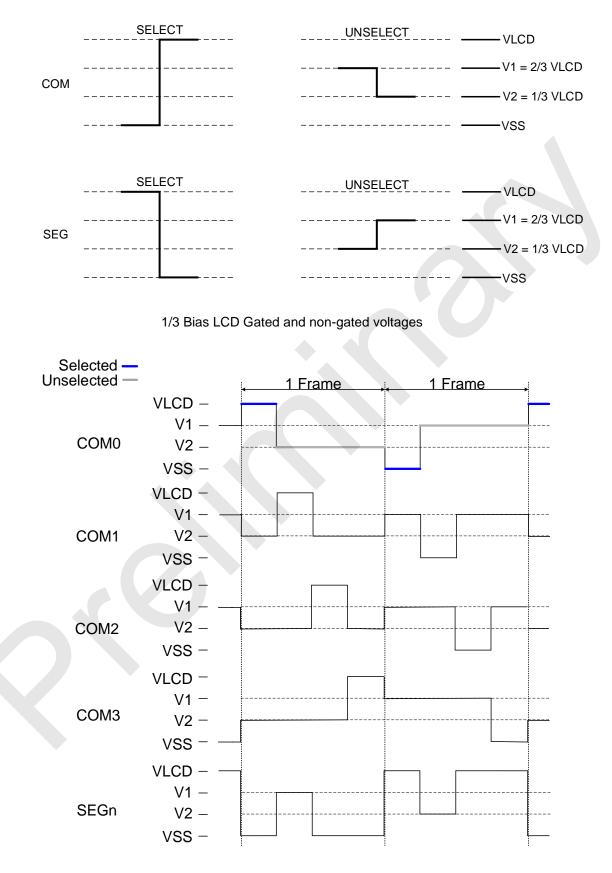

| 15.3.1 1/3Bias LCD Waveform<br>15.3.2 1/4Bias LCD Waveform                                                                                                                                                                                  |     |

| 15.4 LED Waveform                                                                                                                                                                                                                           |     |

| 15.5 LCD/LED Example                                                                                                                                                                                                                        |     |

| 15.5.1 LCD Configuration Demo Program<br>15.5.2 LED Configuration Demo Program                                                                                                                                                              |     |

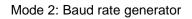

| 16 SERIAL INTERFACE (UART0)                                                                                                                                                                                                                 | 178 |

| 16.1 Baud Rate of Serial Communication                                                                                                                                                                                                      |     |

| 17 SPI/TWI/UART SERIAL INTERFACE (USCI)                                                                                                                                                                                                     |     |

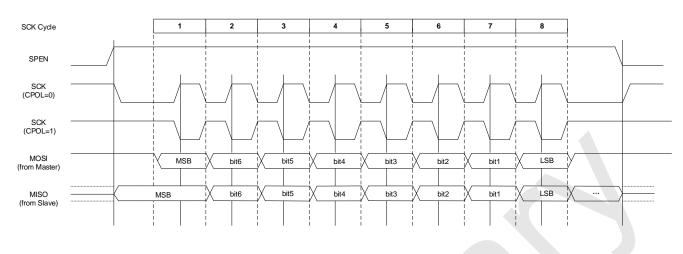

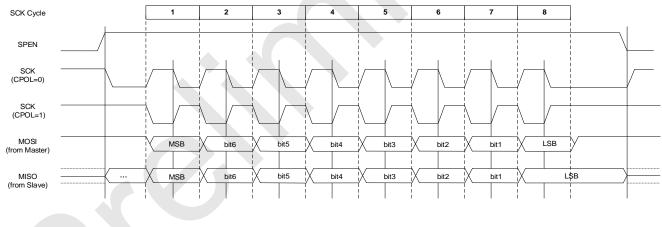

| 17.1 SPI                                                                                                                                                                                                                                    |     |

| 17.1.1 SPI Operation Related Registers                             |     |

|--------------------------------------------------------------------|-----|

| 17.1.2 Signal Description<br>17.1.3 Operating Modes                |     |

| 17.1.3 Operating Modes                                             |     |

| 17.1.5 Error Detection                                             |     |

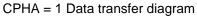

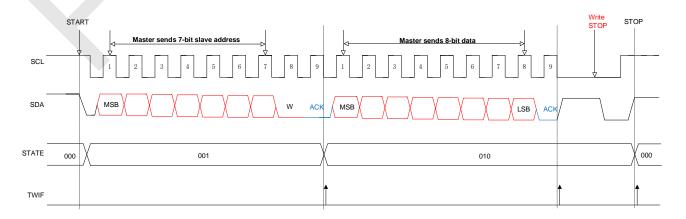

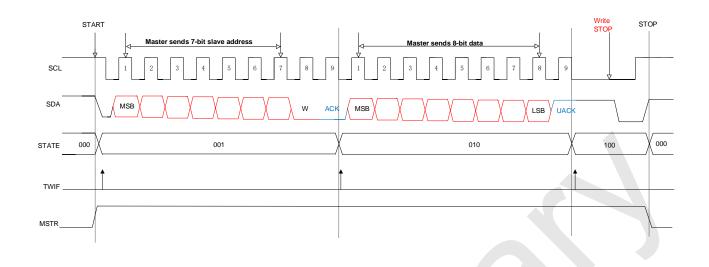

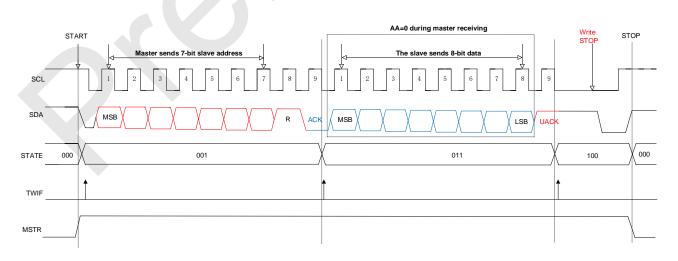

| 17.2 TWI                                                           |     |

| 17.2.1 Signal Description                                          |     |

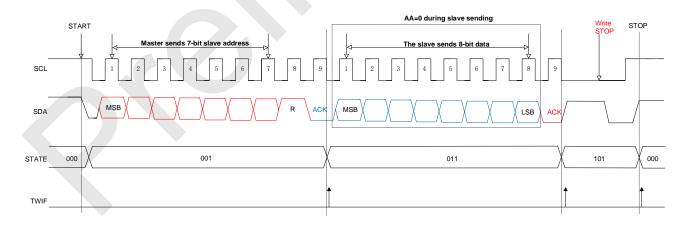

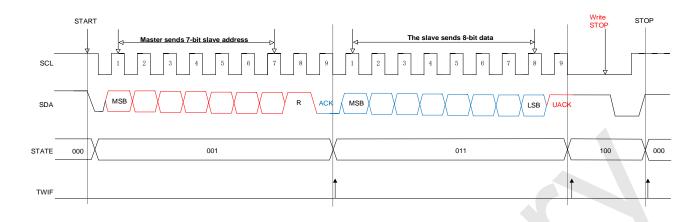

| 17.2.2 Slave Operating Mode                                        |     |

| 17.2.3 Slave Mode Operation Steps                                  |     |

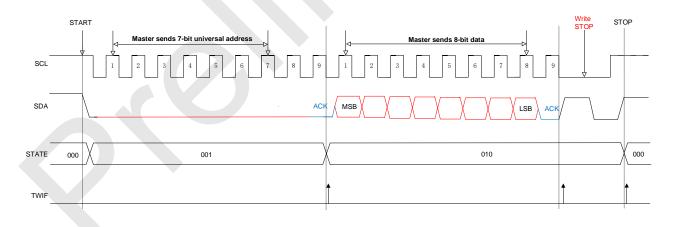

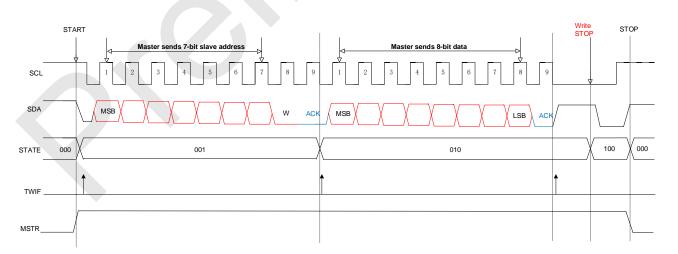

| 17.2.4 Master operating Mode<br>17.2.5 Master Mode Operation Steps |     |

| 17.3 Serial Interface (UART)                                       |     |

| 18 HIGH-SPEED ANALOG-TO-DIGITAL CONVERTER (ADC)                    |     |

| 18.1 ADC-related Registers                                         |     |

| 18.2 ADC Conversion Steps                                          |     |

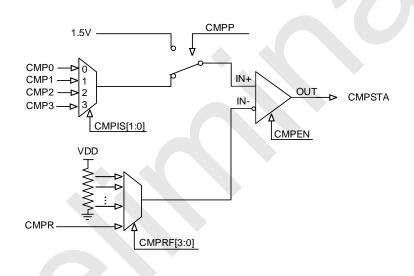

| 19 ANALOG COMPARATOR                                               |     |

| 19.1 Block Diagram of Analog Comparator                            |     |

| 20 HIGH SENSITIVITY TOUCHKEY CIRCUITS                              |     |

| 20.1 Power Consumption of TouchKey Circuits                        |     |

| 21 CRC MODULE                                                      | 224 |

| 21.1 CRC Check Operation Related Registers                         |     |

| 22 MULTIPLIER-DIVIDER UNIT (MDU)                                   | 231 |

| 23 ELECTRICAL CHARACTERISTICS                                      |     |

| 23.1 Absolute Maximum Ratings                                      | 234 |

| 23.2 Recommended Operating Conditions                              |     |

| 23.3 Flash ROM Characteristics                                     |     |

| 23.4 DC Characteristics                                            |     |

| 23.5 AC Characteristics                                            |     |

| 23.6 ADC Characteristics                                           |     |

| 23.7 Analog Comparator Characteristics                             |     |

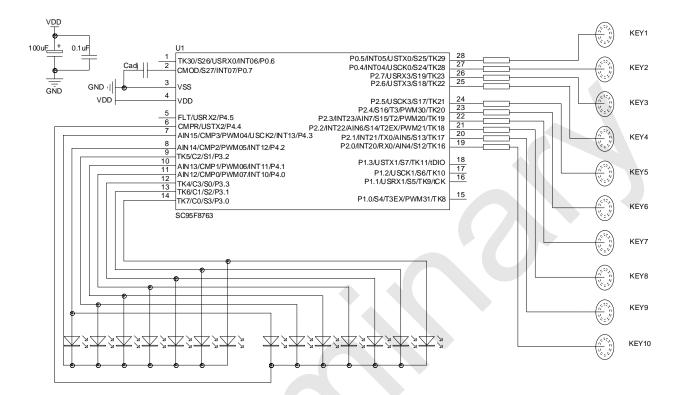

| 24 APPLICATION CIRCUIT                                             |     |

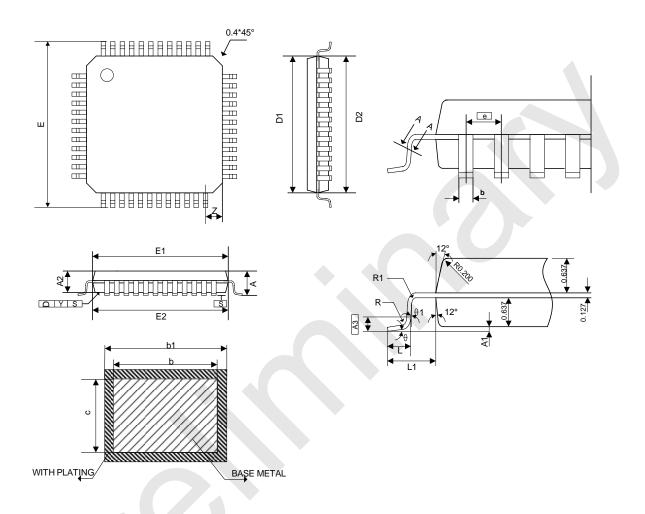

| 25 PACKAGE INFORMATION                                             |     |

| 26 REVISION HISTORY                                                | 259 |

| IMPORTANT NOTICE                                                   |     |

## **3 Pin Description**

## **3.1 Pin Configuration**

Note: In consideration of multiplexing of TK9/TK11 and TK debugging communication ports of the SC95F876X, if it is required to use the TK debugging function, please avoid using TK9/TK11!

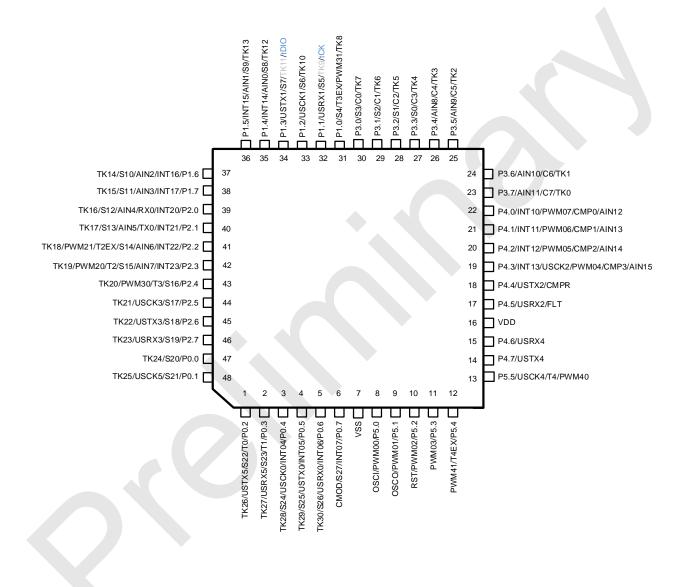

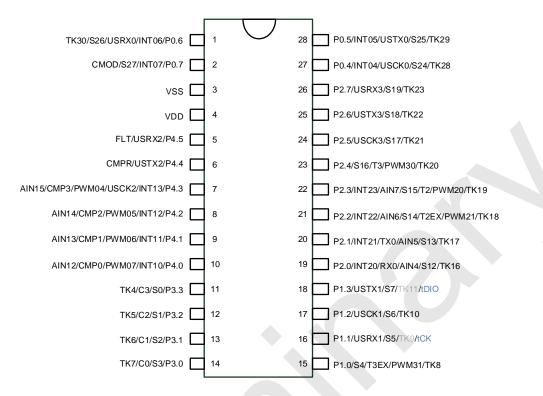

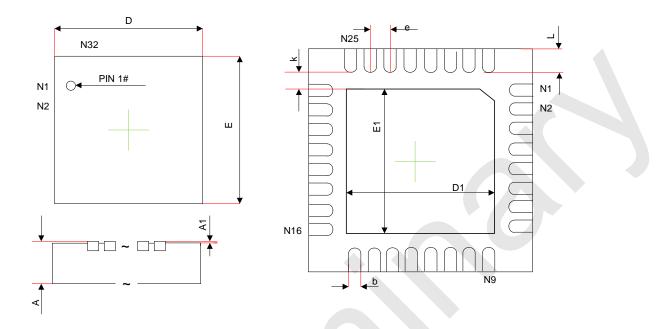

SC95F8767 Pin Diagram

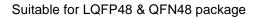

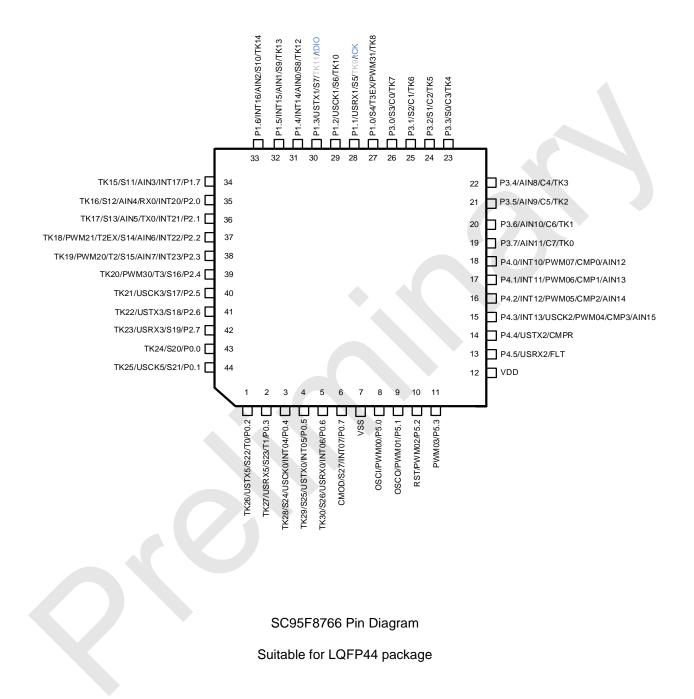

SC95F8765 Pin Diagram

Suitable for LQFP32 & QFN32 package

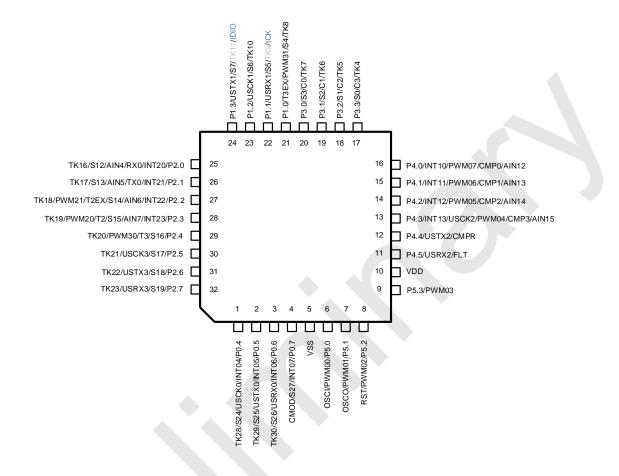

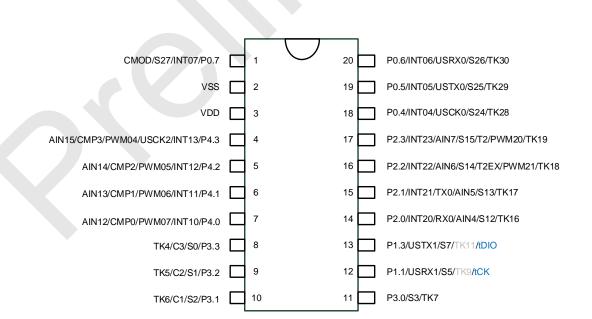

SC95F8763 Pin Diagram

Suitable for SOP28 & TSSOP28 package

SC95F8762 Pin Diagram

#### Suitable for SOP20 & TSSOP20 package

## 3.1.1 48/44 Pin Definition

|    | Pir | n numl | ber |    | Din Nama                      | Turne | Description                                                                                                                       |

|----|-----|--------|-----|----|-------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| 48 | 44  | 32     | 28  | 20 | Pin Name                      | Туре  | Description                                                                                                                       |

| 1  | 1   | -      | -   | -  | P0.2/T0/S22/USTX5/TK26        | I/O   | P0.2: GPIO P0.2<br>T0: Timer/Counter 0 External Input<br>S22: LCD/LED SEG22<br>USTX5: USCI5 MOSI/SDA/TX<br>TK26: TK Channel 26    |

| 2  | 2   | -      | -   | -  | P0.3/T1/S23/USRX5/TK27        | 1/0   | P0.3: GPIO P0.3<br>T1: Timer/Counter 1 External Input<br>S23: LCD/LED SEG23<br>USRX5: USCI5 MISO/RX<br>TK27: TK Channel 27        |

| 3  | 3   | 1      | 27  | 18 | P0.4/INT04/USCK0/S24/T<br>K28 | I/O   | P0.4: GPIO P0.4<br>INT04: Input 4 of external interrupt<br>0USCK0: USCI0 SCK<br>S24: LCD/LED SEG24<br>TK28: TK Channel 28         |

| 4  | 4   | 2      | 28  | 19 | P0.5/INT05/USTX0/S25/TK<br>29 | I/O   | P0.5: GPIO P0.5<br>INT05: Input 5 of external interrupt<br>0USTX0: USCI0 MOSI/SDA/TX<br>S25: LCD/LED SEG25<br>TK29: TK Channel 29 |

| 5  | 5   | 3      | 1   | 20 | P0.6/INT06/USRX0/S26/TK<br>30 | I/O   | P0.6: GPIO P0.6<br>INT06: Input 6 of external interrupt 0<br>USRX0: USCI0 MISO/RX                                                 |

|    |    |   |   |   |                     |       | S26: LCD/LED SEG26<br>TK30: TK Channel 30                                                                                  |

|----|----|---|---|---|---------------------|-------|----------------------------------------------------------------------------------------------------------------------------|

| 6  | 6  | 4 | 2 | 1 | P0.7/INT07/S27/CMOD | I/O   | P0.7: GPIO P0.7<br>INT07: Input 7 of external interrupt 0<br>S27: LCD/LED SEG27<br>CMOD: Touch Key external<br>capacitance |

| 7  | 7  | 5 | 3 | 2 | VSS                 | Power | Ground                                                                                                                     |

| 8  | 8  | 6 | - | - | P5.0/PWM00/OSCI     | I/O   | P5.0: GPIO P5.0<br>PWM00: PWM00 Output<br>OSCI: 32K oscillator output                                                      |

| 9  | 9  | 7 | - | - | P5.1/PWM01/OSCO     | I/O   | P5.1: GPIO P5.1<br>PWM01: PWM01 Output<br>OSCO: 32K oscillator output                                                      |

| 10 | 10 | 8 |   |   | P5.2/PWM02/RST      | I/O   | P5.2: GPIO P5.2<br>PWM02: PWM02 Output<br>RST: Reset pin                                                                   |

| 11 | 11 | 9 |   | - | P5.3/PWM03          | I/O   | P5.3: GPIO P5.3<br>PWM03: PWM03 Output                                                                                     |

| 12 | -  |   | - | - | P5.4/T4EX/PWM41     | I/O   | P5.4: GPIO P5.4<br>T4EX: External capture for Timer4<br>PWM41: PWM41 Output                                                |

| 13 | -  | - | - | - | P5.5/USCK4/T4/PWM40 | I/O   | P5.5: GPIO P5.5<br>USCK4: USCI4 SCK<br>T4: Timer/Counter4 external input                                                   |

|    |    |    |   |   |                                       |       | PWM40: PWM40 Output                                                                                                                                                                  |

|----|----|----|---|---|---------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14 | -  | -  | - | - | P4.7/USTX4                            | I/O   | P4.7: GPIO P4.7<br>USTX4: USCI4 MOSI/SDA/TX                                                                                                                                          |

| 15 | -  | -  | - | - | P4.6/USRX4                            | I/O   | P4.6: GPIO P4.6<br>USRX4: USCI4 MISO/RX                                                                                                                                              |

| 16 | 12 | 10 | 4 | 3 | VDD                                   | Power | Power                                                                                                                                                                                |

| 17 | 13 | 11 | 5 | - | P4.5/USRX2/FLT                        | I/O   | P4.5: GPIO P4.5<br>USRX2: MISO/RX of USCI2<br>FLT: PWM1 fault detection input pin                                                                                                    |

| 18 | 14 | 12 | 6 | - | P4.4/USTX2/CMPR                       | 1/0   | P4.4: GPIO P4.4<br>USTX2: MOSI/SDA/TX of USCI2<br>CMPR: The reference voltage of<br>comparator input.                                                                                |

| 19 | 15 | 13 | 7 | 4 | P4.3/INT13/USCK2/PWM0<br>4/CMP3/AIN15 | I/O   | P4.3: GPIO P4.3<br>INT13: Input 3 of external interrupt 1<br>USCK2: SCK of USCI2<br>PWM04: PWM04 Output<br>CMP3: Analog comparator input<br>channel 3<br>AIN15: ADC input channel 15 |

| 20 | 16 | 14 | 8 | 5 | P4.2/INT12/PWM05/CMP2/<br>AIN14       | I/O   | P4.2: GPIO P4.2<br>INT12: Input 2 of external interrupt 1<br>PWM05: PWM05 Output<br>CMP2: Analog comparator input<br>channel 2<br>AIN14: ADC input channel 14                        |

| 21 | 17 | 15 | 9  | 6 | P4.1/INT11/PWM06/CMP1/<br>AIN13 | I/O | P4.1: GPIO P4.1<br>INT11: Input 1 of external interrupt 1<br>PWM06: PWM06 Output<br>CMP1: Analog comparator input<br>channel 1<br>AIN13: ADC input channel 13 |

|----|----|----|----|---|---------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22 | 18 | 16 | 10 | 7 | P4.0/INT10/PWM07/CMP0/<br>AIN12 | 1/0 | P4.0: GPIO P4.0<br>INT10: Input 0 of external interrupt 1<br>PWM07: PWM07 Output<br>CMP0: Analog comparator input<br>channel 0<br>AIN12: ADC input channel 12 |

| 23 | 19 | -  | -  | - | P3.7/AIN11/C7/TK0               | I/O | P3.7: GPIO P3.7<br>AIN11: ADC Input Channel 11<br>C7: LCD/LED common output 7<br>TK0: TK Channel 0                                                            |

| 24 | 20 | -  | Š  |   | P3.6/AIN10/C6/TK1               | I/O | P3.6: GPIO P3.6<br>AIN10: ADC input channel 10<br>C6: LCD/LED common output 6<br>TK1: TK Channel 1                                                            |

| 25 | 21 |    | -  | - | P3.5/AIN9/C5/TK2                | I/O | P3.5: GPIO P3.5<br>AIN9: ADC input channel 9<br>C5: LCD/LED common output 5<br>TK2: TK Channel 2                                                              |

| 26 | 22 | -  | -  | - | P3.4/AIN8/C4/TK3                | I/O | P3.4: GPIO P3.4<br>AIN9: ADC input channel 8                                                                                                                  |

| Super High-Speed 31-channel TouchKey Flash MCU |

|------------------------------------------------|

|------------------------------------------------|

|    |    |    |    |    |                        |     | C4: LCD/LED common output 4<br>TK3: TK Channel 3                                                                      |

|----|----|----|----|----|------------------------|-----|-----------------------------------------------------------------------------------------------------------------------|

| 27 | 23 | 17 | 11 | 8  | P3.3/S0/C3/TK4         | I/O | P3.3: GPIO P3.3<br>S0: LCD/LED SEG 0<br>C3: LCD/LED common output 3<br>TK4: TK Channel 4                              |

| 28 | 24 | 18 | 12 | 9  | P3.2/S1/C2/TK5         | 1/0 | P3.2: GPIO P3.2<br>S1: LCD/LED SEG 1<br>C2: LCD/LED common output 2<br>TK5: TK Channel 5                              |

| 29 | 25 | 19 | 13 | 10 | P3.1/S2/C1/TK6         | I/O | P3.1: GPIO P3.1<br>S2: LCD/LED SEG 2<br>C1: LCD/LED common output 1<br>TK6: TK Channel 6                              |

| 30 | 26 | 20 | 14 | 11 | P3.0/S3/C0/TK7         | I/O | P3.0: GPIO P3.0<br>S3: LCD/LED SEG 3<br>C0: LCD/LED common output 0<br>TK7: TK Channel 7                              |

| 31 | 27 | 21 | 15 | -  | P1.0/S4/T3EX/PWM31/TK8 | I/O | P1.0: GPIO P1.0<br>S4: LCD/LED SEG 4<br>T3EX: External capture for Timer3<br>PWM31: PWM31 Output<br>TK8: TK Channel 8 |

| 32 | 28 | 22 | 16 | 12 | P1.1/USRX1/S5/TK9/tCK  | I/O | P1.1: GPIO P1.1<br>USRX1: MISO/RX of USCI1                                                                            |

|    |    |    |    |    |                              |     | S5: LCD/LED SEG 5<br>TK9: TK Channel 9, if it is required<br>to use the TK debugging function,<br>please avoid using TK9!                                                                                                                                |

|----|----|----|----|----|------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |    |    |    |                              |     | tCK: Programming and Emulation<br>Clock Pin                                                                                                                                                                                                              |

| 33 | 29 | 23 | 17 | -  | P1.2/USCK1/S6/TK10           | I/O | P1.2: GPIO P1.2<br>USCK1: SCK of USCI1<br>S6: LCD/LED SEG 6<br>TK10: TK Channel 10                                                                                                                                                                       |

| 34 | 30 | 24 | 18 | 13 | P1.3/USTX1/S7/TK11/tDIO      | I/O | P1.3: GPIO P1.3<br>USTX1: MOSI/SDA/TX of USCI1<br>S7: LCD/LED SEG 7<br>TK11: TK channel 11, <b>if it is</b><br><b>required to use the TK debugging</b><br><b>function, please avoid using TK11</b><br><b>tDIO:</b> Programming and Emulation<br>Data Pin |

| 35 | 31 | -  | -  |    | P1.4/INT14/AIN0/S8/TK12      | I/O | P1.4: GPIO P1.4<br>INT14: Input 4 of external interrupt 1<br>AIN0: ADC input channel 0<br>S8: LCD/LED SEG 8<br>TK12: TK Channel 12                                                                                                                       |

| 36 | 32 |    | -  | -  | P1.5/INT15/AIN1/S9/TK13      | I/O | P1.5: GPIO P1.5<br>INT15: Input 5 of external interrupt 1<br>AIN1: ADC input channel 1<br>S9: LCD/LED SEG 9<br>TK13: TK Channel 13                                                                                                                       |

| 37 | 33 | -  | -  | -  | P1.6/INT16/AIN2/S10/TK1<br>4 | I/O | P1.6: GPIO P1.6<br>INT16: Input 6 of external interrupt 1                                                                                                                                                                                                |

|    |    |    |    |    |                                         |     | AIN2: ADC Input Channel 2<br>S10: LCD/LED SEG10<br>TK14: TK Channel 14<br>P1.7: GPIO P1.7                                                                                                       |

|----|----|----|----|----|-----------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38 | 34 | -  | -  | -  | P1.7/INT17/AIN3/S11/TK1<br>5            | I/O | INT17: Input 7 of external interrupt 1<br>AIN3: ADC Input Channel 3<br>S11: LCD/LED SEG11<br>TK15: TK Channel 15                                                                                |

| 39 | 35 | 25 | 19 | 14 | P2.0/INT20/RX0/AIN4/S12/<br>TK16        | 1/0 | P2.0: GPIO P2.0<br>INT20: Input 0 of external interrupt 2<br>RX0: UART0 Receiver<br>AIN4: ADC Input Channel 4<br>S12: LCD/LED SEG12<br>TK16: TK Channel 16                                      |

| 40 | 36 | 26 | 20 | 15 | P2.1/INT21/TX0/AIN5/S13/<br>TK17        | I/O | P2.1: GPIO P2.1<br>INT21: Input 1 of external interrupt 2<br>TX0: UART0 Transmitter<br>AIN5: ADC Input Channel 5<br>S13: LCD/LED SEG13<br>TK17: TK Channel 17                                   |

| 41 | 37 | 27 | 21 | 16 | P2.2/INT22/AIN6/S14/T2E<br>X/PWM21/TK18 | I/O | P2.2: GPIO P2.2<br>INT22: Input 2 of external interrupt 2<br>AIN6: ADC Input Channel 6<br>S14: LCD/LED SEG14<br>T2EX: External capture for Timer2<br>PWM21: PWM21 Output<br>TK18: TK Channel 18 |

| 42 | 38 | 28 | 22 | 17 | P2.3/INT23/AIN7/S15/T2/P<br>WM20/TK19   | I/O | P2.3: GPIO P2.3<br>INT23: Input 3 of external interrupt 2                                                                                                                                       |

|    |    |    |    |   |                        |     | AIN7: ADC Input Channel 7<br>S15: LCD/LED SEG15<br>T2: Timer/Counter2 external input<br>PWM20: PWM20 Output<br>TK19: TK Channel 19 |

|----|----|----|----|---|------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------|

| 43 | 39 | 29 | 23 | - | P2.4/S16/T3/PWM30/TK20 | I/O | P2.4: GPIO P2.4<br>S16: LCD/LED SEG 16<br>T3: Timer/Counter3 external input<br>PWM30: PWM30 Output<br>TK20: TK Channel 20          |

| 44 | 40 | 30 | 24 | - | P2.5/S17/USCK3/TK21    | I/O | P2.5: GPIO P2.5<br>S17: LCD/LED SEG 17<br>USCK3:USCI3 SCK<br>TK21: TK Channel 21                                                   |

| 45 | 41 | 31 | 25 | - | P2.6/S18/USTX3/TK22    | I/O | P2.6: GPIO P2.6<br>S18: LCD/LED SEG 18<br>USTX3: USCI3 MOSI/SDA/TX<br>TK22: TK Channel 22                                          |

| 46 | 42 | 32 | 26 | - | P2.7/S19/USRX3/TK23    | I/O | P2.7: GPIO P2.7<br>S19: LCD/LED SEG 19<br>USRX3: USCI3 MISO/RX<br>TK23: TK Channel 23                                              |

| 47 | 43 |    | -  | - | P0.0/S20/TK24          | I/O | P0.0: GPIO P0.0<br>S20: LCD/LED SEG 20<br>TK24: TK Channel 24                                                                      |

| 48 | 44 | -  | -  | - | P0.1/S21/USCK5/TK25    | I/O | P0.1: GPIO P0.1<br>S21: LCD/LED SEG 21<br>USCK5: USCI5 SCK                                                                         |

|  |  |  |  |  |  | TK25: TK Channel 25 |

|--|--|--|--|--|--|---------------------|

|--|--|--|--|--|--|---------------------|

## 4 Inner Block Diagram

#### SC95F876X BLOCK DIAGRAM

## 5 Flash ROM and SRAM

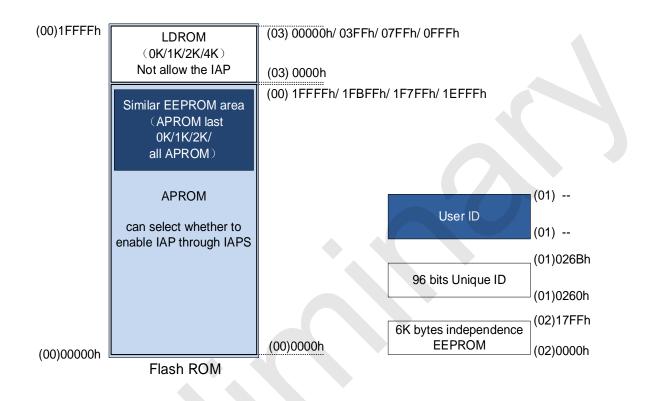

The Flash ROM of SC95F876X is divided into five regions: APROM/LDROM/EEPROM/User ID/Unique ID, as shown in the following figure:

## 5.1 APROM and LDROM

APROM and LDROM are two independent pieces of hardware that divide ROM by LDSIZE[1:0]. They are distinguished by the extended address "00" and "03" set by IAPADE register. They can be programmed and erased by SC LINK PRO.

- The extended address of the APROM area is "00". The maximum size of the area is 128 Kbytes. It supports IAP (In Application Programming) and APROM area allowed IAP operation in Flash can be set to 0K/1K/2K/All APROM by Code Option.

- The extended address of LDROM area is "03", area size 0~4 Kbytes optional. IAP on LDROM is not allowed.

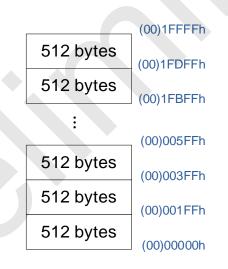

The SC95F876X has 128 Kbytes of Flash ROM, the address is (00)00000H~(00)1FFFFH, "00" in brackets is the extended address, which is set by the IAPADE register. Flash ROM can be programmed and erased by SC LINK PRO provided by SinOne. The characteristics of this 128 Kbytes Flash ROM are as follows:

- Divided into 256 sectors,512 bytes per sector

- Can be rewritten 100,000 times

- The data written-in has more than 100-year preservation life in the ambient temperature of 25°C

- In ICP mode, BLANK, PROGRAM, VERIFY, ERASE and READ functions are supported. The READ function is only valid for ICs with no security encryption function enabled

- Secure Encryption: Optionally enable APROM (128 Kbytes Flash ROM) and LDROM secure encryption

- Support IAP (In Application Programming).

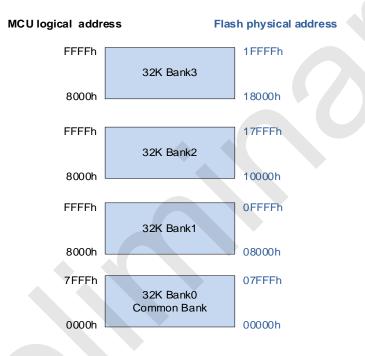

The 128 Kbytes Flash ROM of the SC95F876X is divided into four banks. The structure is as follows:

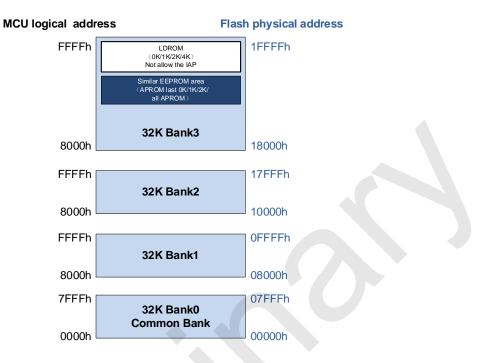

The LDROM and IAP operating areas are defined as follows:

The switch between the four banks of SC95F876X Flash ROM can be implemented through ROMBNK registers:

ROMBNK (DFH) Program Bank switch register (read/write)

| Bit number      | 7 | 6 | 5            | 4            | 3 | 2 | 1           | 0           |

|-----------------|---|---|--------------|--------------|---|---|-------------|-------------|

| Bit<br>Mnemonic | - |   | DATABN<br>K1 | DATABN<br>K0 | - | - | ROMBN<br>K1 | ROMBN<br>K0 |

| R/W             | - |   | R/W          | R/W          | - | - | R/W         | R/W         |

| POR             | х | x | 0            | 1            | х | х | 0           | 1           |

| Bit<br>number | Bit Mnemonic  | Description                                                                                                |

|---------------|---------------|------------------------------------------------------------------------------------------------------------|

| 5~4           | DATABNK [1:0] | Target data address Bank switch bit, controls ROM high 32K address target MOVC and IAP point to the region |

|               |               | 00: Both MOVC and IAP programing are directed at Bank0, where the IAP address range is only 32K            |

|               |               | 01: Both MOVC and IAP programing are directed at Bank0 and Bank1                                           |

|               |               | 10: Both MOVC and IAP programing are directed at Bank0 and Bank2                                           |

|               |               | 11: Both MOVC and IAP programing are directed at Bank0 and Bank3                                           |

|               |               | Note: This control bit is only valid when IAPADE=0x00                                                      |

| 1~0           | ROMBANK[1:0]  | Operation Bank switch bit:                                                                                 |

#### Super High-Speed 31-channel TouchKey Flash MCU

|         |   | 00: Instruction for Bank0;           |

|---------|---|--------------------------------------|

|         |   | 01: Instruction for Bank0 and Bank1; |

|         |   | 10: Instruction for Bank0 and Bank2; |

|         |   | 11: Instruction for Bank0 and Bank3; |

| 7~6,3~2 | - | reserved                             |

SC95F876X has a maximum addressing interval of 64 Kbytes, i.e., two banks, where Bank0 is fixed (interrupt vector etc in Bank0 to prevent disruption after jump) and bank1-3 can be switched. The jump mode of Bank1~3 is as follows: close the interrupt in the user program  $\rightarrow$  jump to Bank0 (the code of switching Bank is stored in Bank0)  $\rightarrow$  modify ROMBNK

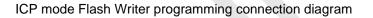

### 5.1.1 Flash ROM Sectors

The SC95F876X has 128 Kbytes of Flash ROM divided into 256 sectors, each sector is 512 bytes, the sector to which the target address belongs will be forcibly erased by the programmer during writing, and then write data; When the user writes, must erasing it before writing.

SC95F876X 128 Kbytes Flash ROM Sectors

## 5.2 6K bytes independent EEPROM

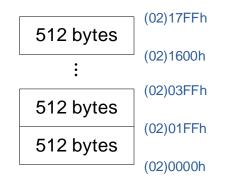

The SC95F876X has 6 Kbytes of independent EEPROM, the address is (02)000H ~ 17FFH, "02" in brackets is the extended address, which is set by the IAPADE register. Independent EEPROM can be rewritten 100,000 times and the data written-in has more than 100-year preservation life in the ambient temperature of 25°C. EEPROM supports blank checking, programming, verification, erasing and reading functions.

EEPROM divided into 12 sectors,512 bytes per sector

#### SC95F876X EEPROM Sectors

Notes: EEPROM can be rewritten 100,000 times. User should not exceed the rated burn times of EEPROM, otherwise there will be exceptions!

## 5.3 96 bits Unique ID Area

The SC95F876X provides an independent Unique ID area. A 96-bit unique code can be pre-programmed before leaving the factory to ensure the uniqueness of the chip. The only way for the user to obtain the serial number is to read the relative address (01)0260H~(01)026BH through the IAP instruction. The Unique ID range is (01)0260H ~ (01)026BH, the "01" in brackets indicates the extended address which is set by the IAPADE register. The specific operation method is as follows:

|  | address regi | ister (near |  |

|--|--------------|-------------|--|

|  |              |             |  |

|  |              |             |  |

IAPADE (E4H) IAP Write to extended address register (Read/Write)

| Bit number      | 7   | 6   | 5   | 4      | 3        | 2   | 1   | 0   |

|-----------------|-----|-----|-----|--------|----------|-----|-----|-----|

| Bit<br>Mnemonic |     |     |     | IAPADE | ER[7: 0] |     |     |     |

| R/W             | R/W | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| POR             | 0   | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

Super High-Speed 31-channel TouchKey Flash MCU

| Bit number | Bit Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                                      |

|------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7~0        | IAPADER[7: 0] | IAP Extended address:<br>0x00: Both MOVC and IAP are for APROM<br>0x01: For the unique ID area, <b>read and write operations are not</b><br><b>allowed, otherwise it may cause an exception!</b><br>0x02: Both MOVC and IAP are for EEPROM<br>0x03: This parameter takes effect only when the LDROM program is<br>operating. Programs running in the LDROM region are allowed to |

|            |               | perform MOVC operations on the LDROM program region. Note:<br>LDROM operation permission is only for MOVC operation,<br>prohibit IAP operation on LDROM, otherwise it will cause<br>unpredictable exceptions!<br>Other: reserved                                                                                                                                                 |

### 5.3.1 Unique ID Read Operating Demo Program In C Language

#include "intrins.h"

unsigned char UniqueID [12];//store UniqueID

unsigned char code \* POINT =0x0260;

unsigned char i;

```

EA = 0; // Disable the global interrupt

IAPADE = 0X01; // Expand address 0x01, select Unique ID area

for(i=0;i<12;i++)

{

UniqueID [i]= *( POINT+i); // Read the value of UniqueID

}

IAPADE = 0X00; // Expand address 0x00, return to Code area

EA = 1; // Enable global interrupt

```

## 5.4 User ID Area

User ID area, whose extended address is (01), is written for user in the factory. Users can read the User ID area, but cannot write the User ID area.

## 5.5 Programming

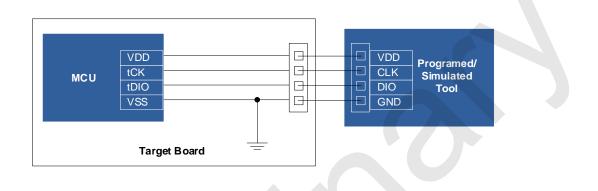

The SC95F876X's Flash ROM can be programmed through tDIO, tCK, VDD, VSS, the specific connection relationship is as follows:

tDIO,tCK is a 2-wire JTAG programming and emulation signal line. Users can configure the mode of these two ports through the Code Option when programming: JTAG Specific Mode and Normal Mode (JTAG specific port is invalid).

#### 5.5.1 JTAG Specific Mode

tDIO,tCK are specific port for programming and emulation, and other functions multiplexed with it are not available. This mode is generally used in the online debugging stage, which is convenient for users to simulate and debug. After the JTAG special mode takes effect, the chip can directly enter the programming or emulation mode without powering on and off again.

#### 5.5.2 Normal Mode (JTAG specific port is invalid)

The JTAG function is not available, and other functions multiplexed with it can be used normally. This mode can prevent the programming port from occupying the MCU pins, which is convenient for users to maximize the use of MCU resources.

Note: When the invalid configuration setting of the JTAG dedicated port is successful, the chip must be completely powered off and then on again to enter the programming or emulation mode, which will affect the programming and emulation in the live mode. SinOne recommends that users select the invalid configuration of the JTAG dedicated port during mass production and programming, and select the JTAG mode during the development and debugging phase.

#### Code Option register:

### OP\_CTM1 (C2H@FFH) Code Option register1 (read/write)

| Bit number | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|---|---|---|---|---|---|---|---|

|------------|---|---|---|---|---|---|---|---|

### Super High-Speed 31-channel TouchKey Flash MCU

| Bit<br>Mnemonic | VREF | S[1: 0] | OP_BL | DISJTG | IAPS[1: 0] |     | LDSIZE[1:0]<br>- |

|-----------------|------|---------|-------|--------|------------|-----|------------------|

| R/W             | R/W  | R/W     | R/W   | R/W    | R/W        | R/W | R                |

| POR             | n    | n       | n     | n      | n          | n   | n n              |

| Bit number | Bit Mnemonic | Description                                                                                                                                                  |

|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4          | DISJTG       | IO/JTAG port switching control<br>0 : JTAG mode is enabled, P1.1 and P1.3 can only be used as<br>tCK/tDIO. Recommended settings during R&D and commissioning |

|            |              | 1 : Normal mode (Normal), JTAG function is invalid. The recommended setting for the mass production burning stage.                                           |

## 5.6 In Application Programming (IAP)

Application Programming (IAP) operations can be carried out in the APROM of SC95F876X (0K, 1K, 2K, or all APROM ranges are optional) and 6K bytes EEPROM. Users can implement remote program updates through IAP operations. You can also obtain Unique ID field or User ID field information via IAP reads. Before IAPS write data, you must erase the Sector to which the target address belongs. The length of a Sector is 512 bytes.Flash ROM is divided into 256 sectors from (00)000H~(00)1FFFFH. The "00" in brackets is the expanded address set by the IAPADE register:

NOTE:

1. During the IAP erase/write process, the CPU holds the program counter, and after the IAP erase/write is complete, the program counter continues to execute subsequent instructions.

2. IAP operation in APROM area has certain risks, users need to take corresponding security measures in the software, if improper operation may cause user program rewriting! This feature is not recommended unless it is required by the user (for example, for remote application updates).

3. The EEPROM erasure count is 100,000. Do not exceed the rated EEPROM erasure count; otherwise, an exception may occur.

The user can select the IAP region range of APROM through Customer Option during programming, or set the IAP region of APROM through IAPS control bit in the program. The relevant registers are as follows: **OP\_CTM1** (C2H@FFH) Code Option Register 1(Read/write)

| Bit number      | 7    | 6      | 5     | 4      | 3    | 2      | 1     | 0            |

|-----------------|------|--------|-------|--------|------|--------|-------|--------------|

| Bit<br>Mnemonic | VREF | S[1:0] | OP_BL | DISJTG | IAPS | 5[1:0] | LDSIZ | E[1:0]-<br>- |

| R/W             | R/W  | R/W    | R/W   | R/W    | R/W  | R/W    | _     | R            |

| POR             | n    | n      | n     | n      | n    | n      | n     | n            |

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3~2        | IAPS[1: 0]   | <ul> <li>IAP spatial range selection</li> <li>00: Full Flash ROM not allows IAP operation</li> <li>01: Last 1K Flash ROM allows IAP operation</li> <li>10: Last 2K Flash ROM allows IAP operation</li> <li>11: Full Flash ROM allows IAP operation</li> <li>Note:</li> <li>1. The above setting items are invalid in BootLoader mode. The BootLoader program can perform IAP operation on the entire Flash ROM area.</li> <li>2. LDROM does not allow IAP operation under any circumstances.</li> </ul> |

Super High-Speed 31-channel TouchKey Flash MCU

### 5.6.1 IAP Operation Related Register

| Symbol | Address | Description                                  | 7             | 6            | 5          | 4      | 3       | 2 | 1   | 0       | POR       |

|--------|---------|----------------------------------------------|---------------|--------------|------------|--------|---------|---|-----|---------|-----------|

| IAPKEY | F1H     | Data protection<br>register                  |               |              | 14         | APKE Y | ′[7: 0] |   |     |         | 00000000b |

| IAPADL | F2H     | IAP write address<br>low register            |               | IAPADR[7: 0] |            |        |         |   |     |         | 00000000b |

| IAPADH | F3H     | IAP write address<br>high register           | IAPADR[15: 8] |              |            |        |         |   |     |         | 0000000b  |

| IAPADE | F4H     | IAP write to<br>extended address<br>register |               |              | IA         | PADE   | R[7: 0  | 1 |     |         | 0000000b  |

| IAPDAT | F5H     | IAP data register                            |               |              | 14         | APDA1  | [7: 0]  |   |     |         | 0000000b  |

| IAPCTL | F6H     | IAP control register                         | BTL<br>D      | -            | SERAS<br>E | PRG    | -       | - | CMD | 0[1: 0] | 0x00xx00b |

#### IAPKEY (F1H) Data Protection Register (Read/Write)

| Bit number      | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Bit<br>Mnemonic | IAPKEY[7: 0] |     |     |     |     |     |     |     |

| R/W             | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR             | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Bit Number | Bit Mnemonic | Description                                        |

|------------|--------------|----------------------------------------------------|

| 7~0        | IAPKEY[7: 0] | Open IAP function and operation time limit setting |

## Super High-Speed 31-channel TouchKey Flash MCU

|  | Write a value n greater than or equal to 0x40, which represents:                                   |

|--|----------------------------------------------------------------------------------------------------|

|  | 1.Enable the IAP function;                                                                         |

|  | 2.If no IAP write command is received after n system clocks, the IAP function is turned off again. |

### IAPADL (F2H) IAP Write Address Low Register (read/write)

| Bit number      | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-----------------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| Bit<br>Mnemonic |     | IAPADR[7: 0] |     |     |     |     |     |     |  |

| R/W             | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

| POR             | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| Bit Number | Bit Mnemonic | Description                              |

|------------|--------------|------------------------------------------|

| 7~0        | IAPADR[7: 0] | IAP writes the low 8 bits of the address |

### IAPADH (F3H) IAP Write Address High Register (read/write)

| Bit number      | 7   | 6             | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------|-----|---------------|-----|-----|-----|-----|-----|-----|

| Bit<br>Mnemonic |     | IAPADR[15: 8] |     |     |     |     |     |     |

| R/W             | R/W | R/W           | R/W | R/W | R/W | R/W | R/W | R/W |

| POR             | 0   | 0             | 0   | 0   | 0   | 0   | 0   | 0   |

|  | Bit Number | Bit Mnemonic | Description |

|--|------------|--------------|-------------|

|--|------------|--------------|-------------|

## Super High-Speed 31-channel TouchKey Flash MCU

| 7~0 | IAPADR[15: 8] | IAP writes the high 8 bits of the address |

|-----|---------------|-------------------------------------------|

|-----|---------------|-------------------------------------------|

### IAPADE (F4H) IAP Write to Extended Address Register (Read/Write)

| Bit number      | 7   | 6   | 5   | 4      | 3        | 2   | 1   | 0   |

|-----------------|-----|-----|-----|--------|----------|-----|-----|-----|

| Bit<br>Mnemonic |     |     |     | IAPADI | ER[7: 0] |     |     |     |

| R/W             | R/W | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| POR             | 0   | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

| Bit Number | Bit Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7~0        | IAPADER[7: 0] | <ul> <li>IAP extended address:</li> <li>0x00: Both MOVC and IAP are for code</li> <li>0x01: The Unique ID area is read but cannot be written 0x02: Both MOVC and IAP are for independent EEPROM</li> <li>0x03: MOVC is performed in the LDROM region (Note: only MOVC can be used, not IAP, this item is only valid for LDROM operation, APROM operation this item is not valid!)</li> <li>Other: reserved</li> </ul> |

## IAPDAT (F5H) IAP Data Register (read/write)

| Bit number      | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-----------------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| Bit<br>Mnemonic |     | IAPDAT[7: 0] |     |     |     |     |     |     |  |

| R/W             | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

## Super High-Speed 31-channel TouchKey Flash MCU

| POR 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|-------|---|---|---|---|---|---|---|

|-------|---|---|---|---|---|---|---|

| Bit number | Bit<br>Mnemonic | R/W |                     | Description |

|------------|-----------------|-----|---------------------|-------------|

| 7~0        | IAPDAT[7:0]     | R/W | Data written by IAP |             |

### IAPCTL (F6H) IAP Control register (Read/Write)

| Bit number   | 7    | 6 | 5      | 4   | 3 | 2 | 1         | 0   |

|--------------|------|---|--------|-----|---|---|-----------|-----|

| Bit Mnemonic | BTLD | - | SERASE | PRG | - |   | CMD[1: 0] |     |

| R/W          | R/W  | - | R/W    | RW  | - | - | R/W       | R/W |

| POR          | 0    | X | 0      | 2   | x | х | 0         | 0   |

## 5.6.2 IAP Operation process

Please refer to the "SC95FXX6X\_SC95FXX1XB IAP Operation Library Documentation Pack" for the IAP operation process of SC95F876X.

## 5.6.3 IAP Operating Demo Program In C Language

The header files shared by the following routines are as follows:

#include "intrins.h"

unsigned int IAP\_Add;

unsigned char IAP\_Data;

unsigned char code \* POINT =0x0000;

### IAP operation: read data:

EA = 0; // Close global interrupt

SC95F8767/8766/8765/8763/8762 Super High-Speed 31-channel TouchKey Flash MCU

IAPADE = 0X00;

//The extended address is 0x00, selectFlash ROM

IAP\_Data = \*( POINT+IAP\_Add); //Read the value of IAP\_Add toIAP\_Data

EA = 1; // Open global interrupt

#### IAP operation: erase and write data:

Please refer to "SC95FXX6X\_SC95FXX1XB IAP Operation Library Kit" if you want to implement IAP erasable operation.

### 5.6.4 IAP Operation notes

- 1. The user must erase the target sector before writing.

- 2. IAP operation in APROM area has certain risks, users need to take corresponding security measures in the software, if improper operation may cause user program rewriting! This feature is not recommended unless required (for remote application updates, for example);

- When programming IC, if "APROM zone prevents IAP operation" is selected through Code Option, then IAPADE [7:0]=0x00 (APROM zone is selected), IAP cannot be operated, that is, data cannot be written, data can only be read by MOVC instruction;

- 4. When IAPADE is not 0x00, the MOVC and write target is non-APROM region. At this time, if there is an interrupt and MOVC operation occurs in the interrupt, the result of MOVC will be wrong and the program will run abnormally. To avoid this situation, if IAPADE is not 0x00 during IAP operation, it is important to turn off total interrupt (EA=0) before operation, and set IAPADE = 0x00 after operation before turning on total interrupt (EA=1);

- 5. During the IAP wipe/write process, the CPU holds the program counter, and the program counter only continues to execute subsequent instructions after the IAP wipe/write is complete;

- 6. The EEPROM erasure count is 100,000. Do not exceed the rated EEPROM erasure count; otherwise, an exception may occur!

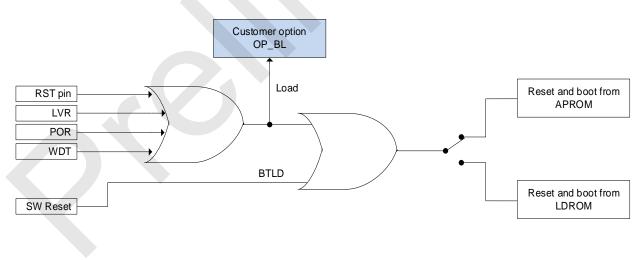

## 5.7 BootLoader

The LDROM is used to store the bootLoader code. LDROM supports blank checking (BLANK), programming (PROGRAM), verifying (VERIFY), erasing (ERASE) and reading (READ) functions in ICP mode.

Users can realize ISP (In System Programing) function through LDROM: when ISP is executed, IC runs the boot code In LDROM area. When the boot code is executed, IC receives new program code through serial port, and then programs the received code into user code area through IAP command.

The LDROM has four address ranges:

- (03)0000H~(03)0000H (without LDROM)

- (03)0000H~(03)03FFH (1K)

- (03)0000H~(03)07FFH (2K)

- (03)0000H~(03)0FFFH (4K)

Where: "03" in the brackets above indicates the extended address, which is set by LDSIZE [1:0].

## 5.7.1 BootLoader Mode operation related registers

### OP\_CTM1 (C2H@FFH) Code Option Register1 (Read/Write)

| Bit number      | 7    | 6       | 5     | 4      | 3         | 2   | 1            | 0 |

|-----------------|------|---------|-------|--------|-----------|-----|--------------|---|

| Bit<br>Mnemonic | VREF | S[1: 0] | OP_BL | DISJTG | IAPS[1:0] |     | LDSIZE [1:0] |   |

| R/W             | R/W  | R/W     | R/W   | R/W    | R/W       | R/W | Only read    |   |

| POR             | n    | n       | n     | n      | n         | n   | n            | n |

| Bit Number | Bit Mnemonic | Description                                                                 |

|------------|--------------|-----------------------------------------------------------------------------|

| 5          | OP_BL        | Program run area control bit<br>0: After the chip is reset, it enters APROM |

## Super High-Speed 31-channel TouchKey Flash MCU

|     |              | 1: After the chip is reset, it enters LDROM                                                  |                           |                |  |  |

|-----|--------------|----------------------------------------------------------------------------------------------|---------------------------|----------------|--|--|

|     |              | ① The MOVC and IAP restrictions for APROM are as follows:                                    |                           |                |  |  |

|     |              | Operation                                                                                    | Is it operable?           |                |  |  |

|     |              | LDROM MOVC                                                                                   | x                         |                |  |  |

|     |              | APROM MOVC                                                                                   | Only the first 256 bytes  | cannot be MOVC |  |  |

|     |              | LDROM IAP                                                                                    | ×                         |                |  |  |

|     |              | APROM IAP                                                                                    | $\checkmark$              |                |  |  |

|     |              | ② The MOVC and IAP restrictions for LDROM are as follows:                                    |                           |                |  |  |

|     |              | Operation Is it opera                                                                        |                           |                |  |  |

|     |              | LDROM MOVC                                                                                   |                           | $\checkmark$   |  |  |

|     |              | APROM MOVC                                                                                   |                           | $\checkmark$   |  |  |

|     |              | LDROM IAP                                                                                    |                           | ×              |  |  |

|     |              | ALL APROM IAP, not                                                                           | restricted by IAPRANGE    | $\checkmark$   |  |  |

| 1~0 | LDSIZE [1:0] | LDROM space range se                                                                         | lection                   |                |  |  |

|     |              | 00: None LDROM, the APROM address is 00000H~1FFFFH                                           |                           |                |  |  |

|     |              | 01: The last 1K APROM area of the Flash ROM is LDROM, and the APROM address is 00000H~1FBFFH |                           |                |  |  |

|     |              | 10: The last 2K APROM area of the Flash ROM is LDROM, and the APROM address is 00000H~1F7FFH |                           |                |  |  |

|     |              | 11: The last 4K APROM area of the Flash ROM is LDROM, and the APROM address is 00000H~1EFFFH |                           |                |  |  |

|     |              | NOTE: LDROM not allo                                                                         | ow IAP operation in anywa | ays            |  |  |

### IAPKEY (F1H) Data Protection Register (Read/Write)

| Bit number         7         6         5         4         3         2         1 | 0 |

|----------------------------------------------------------------------------------|---|

|----------------------------------------------------------------------------------|---|