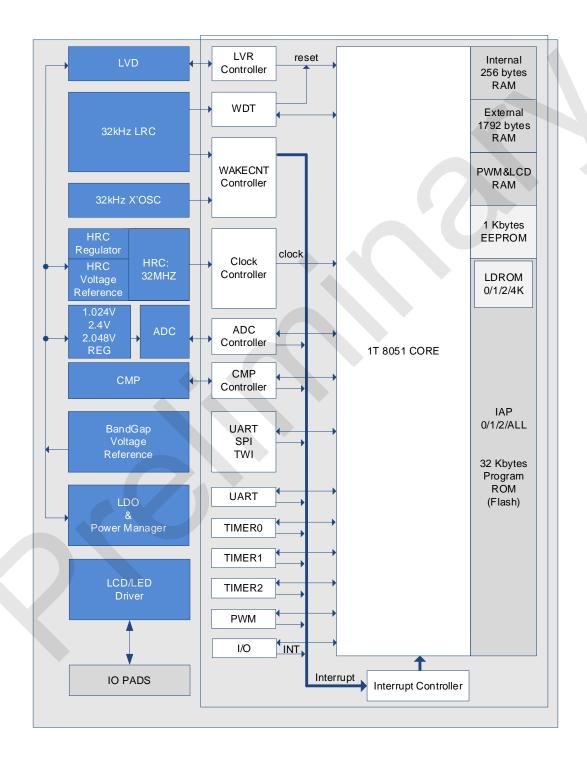

Super High-speed 1T 8051 Core Flash MCU, 2 Kbytes SRAM, 32 Kbytes Flash ROM, 1 Kbytes Independent EEPROM, 12-bit ADC, 1 Analog Comparator, LCD/LED Driver, 12-bit PWM, 3 Timers, MDU, UART, SSI, Check Sum Module

### 1 General Description

SC92F7597SC92F7597/7596/7595/7593 The (hereinafter referred to as the SC92F759X) is a series of enhanced 1T 8051 core industry-standard Flash Microcontroller unit (MCU) is compatible with the standard 8051 series.

The SC92F759X is integrated with 32 Kbytes Flash ROM, 256 bytes SRAM, external 1792 bytes RAM, 1 Kbytes independent EEPROM, up to 46 Generalpurpose I/Os (GPIO), 16 external interrupters, three 16-bit timers, 17-channel 12-bit high-precision ADC, 1 analog comparator, 4-channel 12-bit PWM, one 16 \* 16-bit hardware Multiplier-Divide Unit (MDU), internal ±2% high-precision high-frequency 32MHz oscillator and ±4% precision low-frequency 32kHz oscillator, can be connected to external 32.768kHz oscillators crystal and 1 UART. (UART/TWI/SPI). To improve the reliability and simplify the circuit design, the SC92F759X is also built in with 4-level optional LVR voltage, 1.024V/ 2.4V/ 2.048V ADC reference voltage, low-power WDT and other high-reliability circuits.

The SC92F759X features excellent anti-interference performance, which make it possible to be widely applied to industrial control system, such as Internet of Things, intelligent home appliances, Charger, power supply, model airplane, interphone, wireless communication, gaming peripherals and consumer applications.

### 2 Features

#### **Operating Conditions**

Voltage Range: 2.0V~5.5V

Temperature Range: -40°C ~ +105°C

#### **EMS**

**ESD**

HBM: MIL-STD-883J Class 3A

MM: JEDEC EIA/JESD22-A115 Class C

#### EFT

EN61000-4-4 Level 4

#### **CPU**

8-bit 1T 8051 core CMOS microcontroller, instruction set fully compatible with MCS-51

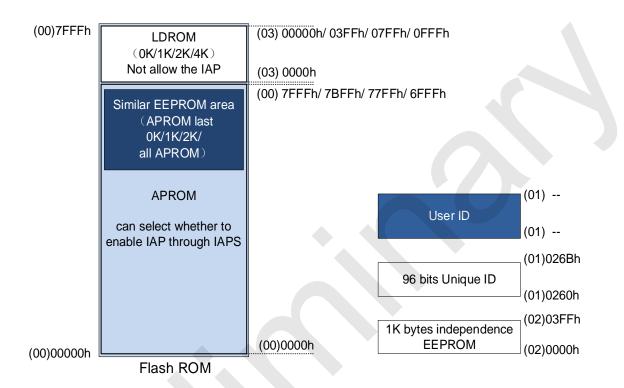

#### Flash ROM

- 32 Kbytes Flash ROM

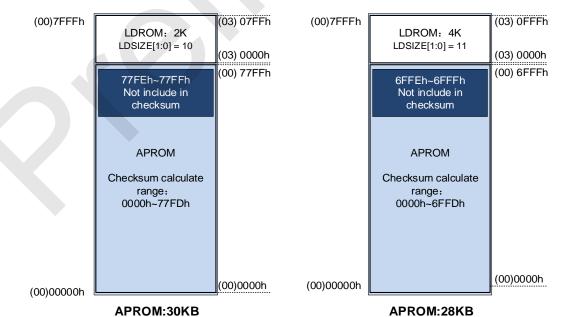

- The APROM area can be set to the range of IAP operation to 0K / 1K / 2K/all APROM through the Code Option setting item

- LDROM:

- Used to store the user's BootLoader boot code

- The LDROM can be set to 0K/1K/2K/4K through the Code Option setting item

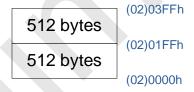

- EEPROM:

- Independent 1K bytes EEPROM

- 100,000 times of writing, and more than 100 years of storage life at room temperature

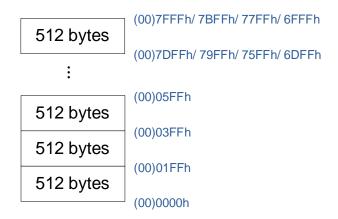

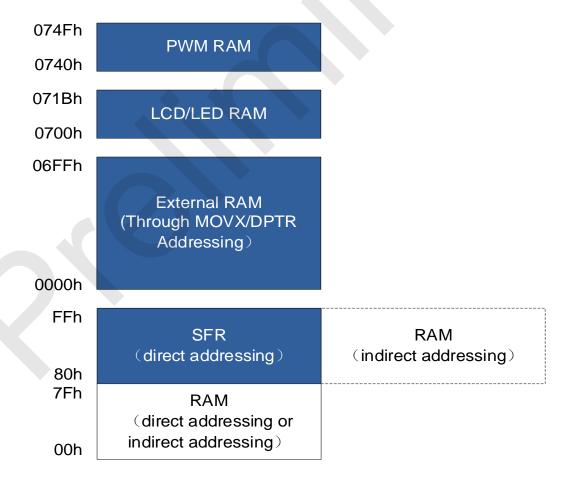

#### SRAM:

- Internal 256 bytes

- 1792 Bytes Indirect Access RAM (XRAM)

- Additional 44 bytes PWM&LCD RAM

#### **Unique ID:**

96 bits Unique ID, which stores the unique identifier of an IC

#### System Clock (f<sub>SYS</sub>)

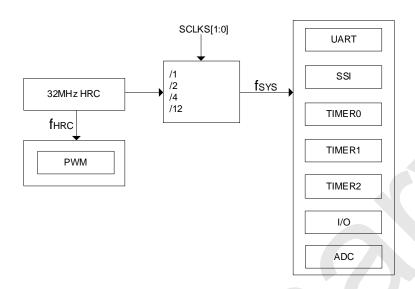

Built-in high frequency 32MHz oscillator (f<sub>HRC</sub>)

V0.1

#### **Super High-Speed 1T 8051 Core Flash MCU**

- The system clock frequency (fsys) of the IC can be selected and set by the programmer as: 32/16/8/2.66 MHz @2.0~5.5V

- Frequency Error: Across (2.0~5.5V) and (-20 ~ 85°C) application environment, the frequency error is not more than ±2%

- The system clock can be automatically calibrated by 32.768kHz external crystal oscillator, after calibration HRC accuracy can be infinitely close to the accuracy of external 32.768kHz crystal oscillator.

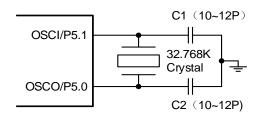

#### **Built-in low-frequency crystal oscillator circuit:**

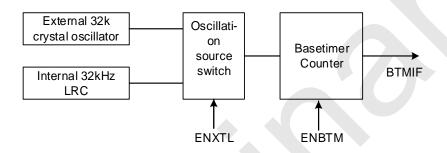

32.768k oscillator can be connected externally as a Base Timer clock source, and wake up STOP

#### Built-in low-frequency 32kHz oscillator (LRC):

- Used as the clock source for Base Timer and WDT, and wake up STOP

- Frequency Error: Across (4.0~5.5V) and (-20 ~ 85℃) application environment, after the register correction frequency error is not more than ±4%

#### Low-voltage Reset (LVR)

- 4 options of reset voltage: 4.3/3.7/ 2.9/1.9V

- The default value can be selected by the Code Option

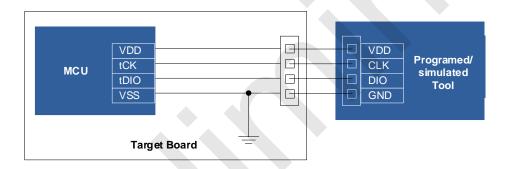

#### Flash Programming and Emulation

- 2-wire JTAG programming and emulation interface

- Jtag-specific mode and regular mode can be set through Code Option

#### Interrupts (INT)

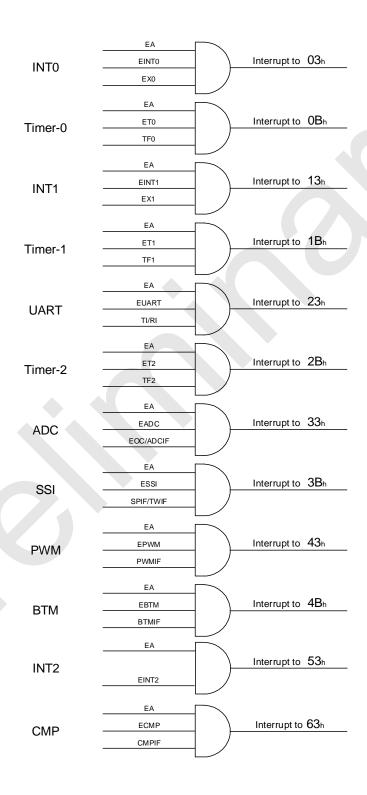

- Up to 12 interrupt sources including Timer0~Timer2, INT0~2, ADC, PWM, UART, SSI, Base Timer, CMP

- External interrupt contains 3 interrupt vectors, 16 interrupt ports. All can set up rising edge, falling edge, dual edge interrupt.

- Two-level interrupt priority capability

#### **Digital Peripheral:**

- Up to 46 bidirectional independently controllable I/O ports

- The pull-up resistors can be set independently

- All I/Os have large sink current drive capability (50mA)

- P0~P3L (P3.0/1/2/3) port source drive capability is divided into four levels

- Built-in WDT, optional clock frequency division ratio

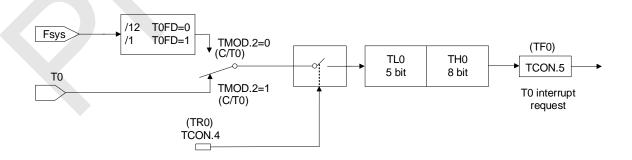

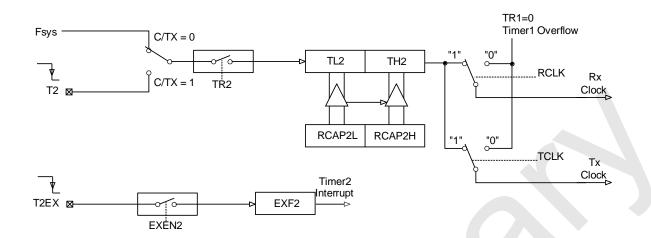

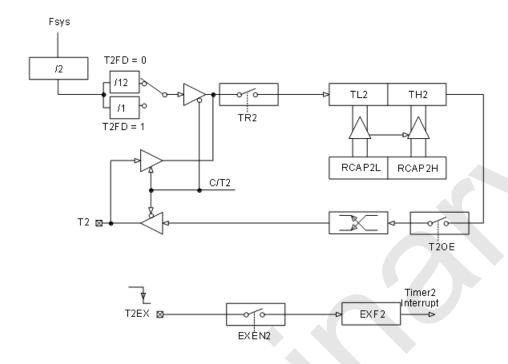

- 3 standard 80C51 timers: Timer0, Timer1, and Timer2. Timer2 provides the Capture function

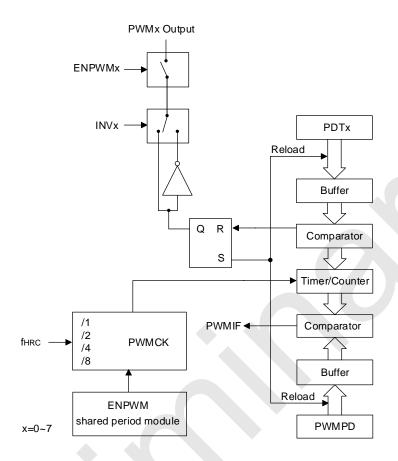

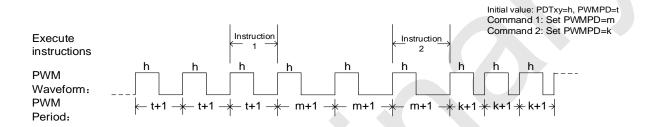

- 4-channel 12-bit PWM

- 1 independent UART communication port

- 1 UART/SPI/TWI communication interfaces (SSI)

- 1 integrated with 16 \* 16-bit hardware Multiplier-Divide Unit (MDU)

#### LCD/LED driver:

- Choose one of two LCD/LED drive functions, share registers and I/O ports

- LED driver: 8 X 24, 6 X 26, 5 X 27, or 4X 28 segments

- LED segment port source drive capability is selectable in four levels

- LCD driver: 8 X 24, 6 X 26, 5 X 27, or 4X 28 segments

- SC92F7595 without LCD/LED Driver

#### **Analog Peripheral**

- 17-channel 12-bit ±2 LSB ADC

- Built-in 1.024V, 2.4V and 2.048V reference voltages

- The ADC reference voltages is optional: V<sub>DD</sub>, 1.024V, 2.4V, 2.048V

Page 2 of 198 V0.1

#### Super High-Speed 1T 8051 Core Flash MCU

- One internal channel can measure the voltage of the power supply

- The sampling clock of the ADC circuit follows the fsys

- ADC conversion can be set to complete the interrupt

- 1 Analog Comparator

- The positive input of the analog comparator can be selected as:

- ◆ CMP0-3 One of four input ports

- ♦ Internal 1.5V reference voltage

- 4-channel input and 1-channel reference voltage input

- Can awaken the STOP mode

- 16-level optional comparison voltage

#### **Power Saving Mode**

- IDLE Mode: can be woken up by any interrupt

- STOP Mode: can be woken up by INT0~2, Base Timer, CMP.

Page 3 of 198 V0.1

# Naming Rules for 92 Series Products

| Name | SC | 92 | F | 7 | 5   | 9 | 7 | Х | Р | 48  | R   |

|------|----|----|---|---|-----|---|---|---|---|-----|-----|

| S/R  | 1  | 2  | 3 | 4 | (5) | 6 | 7 | 8 | 9 | 100 | 11) |

| S/R  | Meaning                                                                                           |

|------|---------------------------------------------------------------------------------------------------|

| 1    | SinOne Chip abbreviation                                                                          |

| 2    | Name of product series                                                                            |

| 3    | Product Type (F: Flash MCU)                                                                       |

| 4    | Serial Number: 7: GP Series, 8: TK series                                                         |

| (5)  | ROM Size: 1 for 2K, 2 for 4K, 3 for 8K, 4 for 16K, 5 for 32K                                      |

| 6    | Subseries Number.: 0 ~ 9, A ~ Z                                                                   |

| 7    | Number of Pins: 0: 8pin, 1: 16pin,2: 20pin,3: 28pin,5: 32pin,6: 44pin,7: 48pin,8: 64pin,9: 100pin |

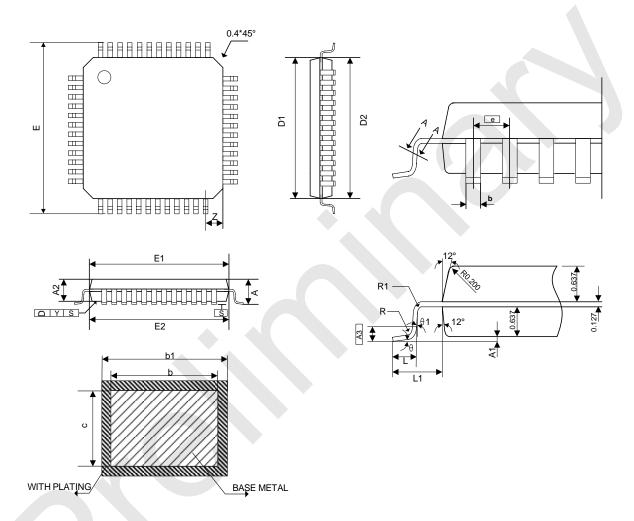

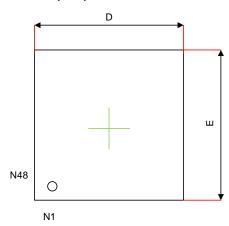

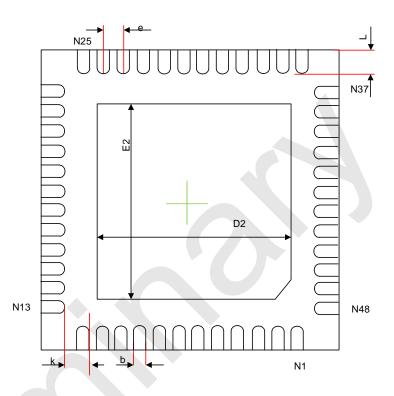

| 8    | Package Type: (D: DIP; M: SOP; X: TSSOP; F: QFP; P: LQFP; Q: QFN; K: SKDIP)                       |

| 9    | Number of Pins.                                                                                   |

| (10) | Number of Pins.                                                                                   |

| (11) | Packaging Mode: (U: Tube; R: Tray; T: Reel)                                                       |

Page 4 of 198 V0.1

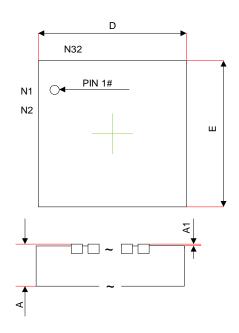

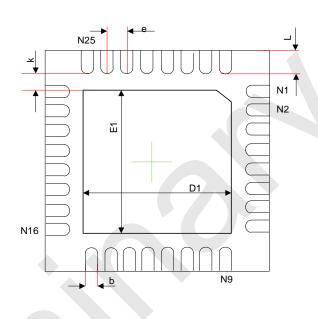

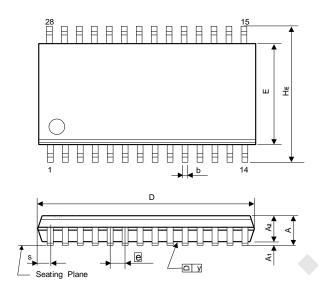

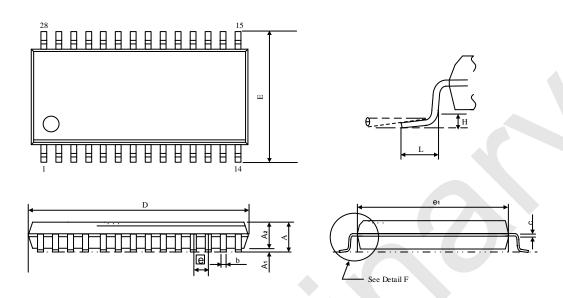

# **Ordering Information**

| PRODUCT ID    | PACKAGE | PACK |

|---------------|---------|------|

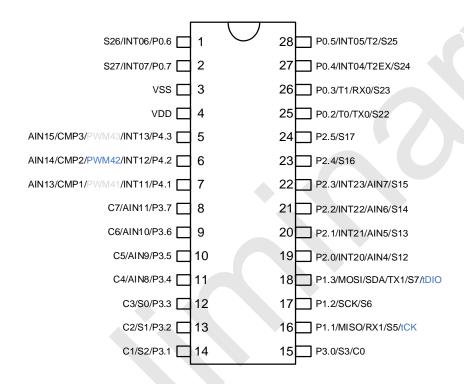

| SC92F7593M28U | SOP28   | TUBE |

| SC92F7593X28U | TSSOP28 | TUBE |

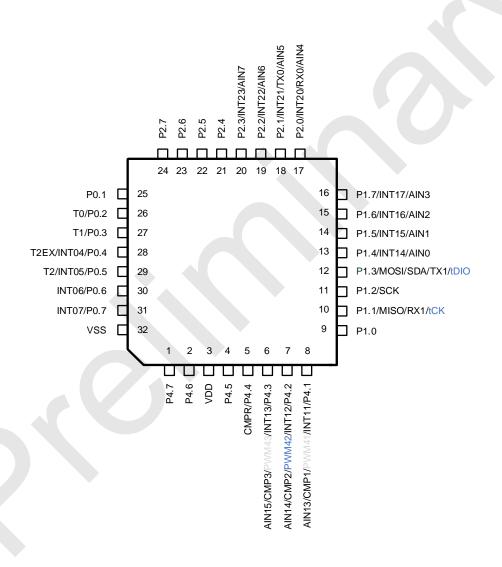

| SC92F7595Q32R | QFN32   | TRAY |

| SC92F7595P32R | LQFP32  | TRAY |

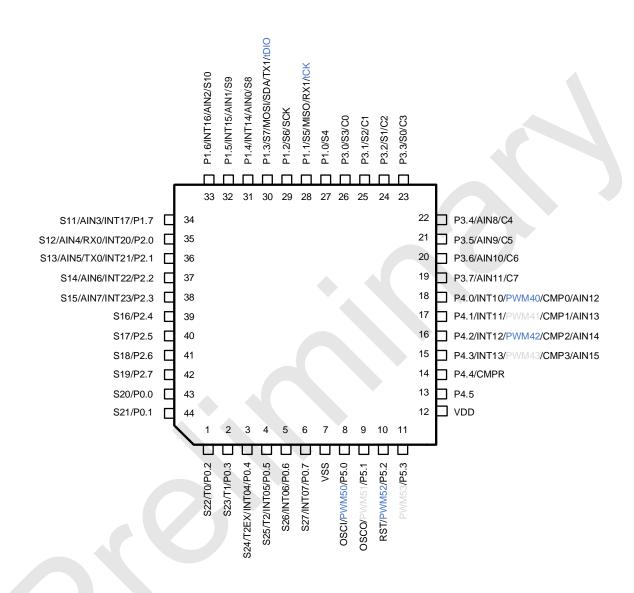

| SC92F7596P44R | LQFP44  | TRAY |

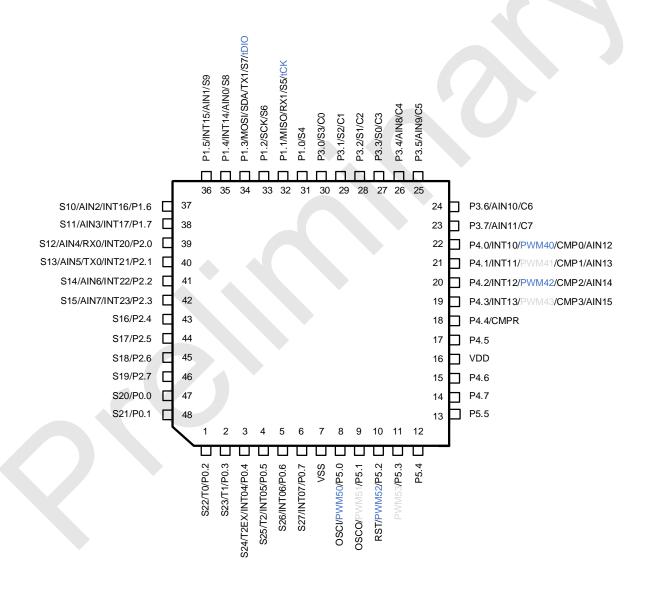

| SC92F7597Q48R | QFN48   | TRAY |

| SC92F7597P48R | LQFP48  | TRAY |

Page 5 of 198 V0.1

### Super High-Speed 1T 8051 Core Flash MCU

### **Contents**

| 1 GENERAL DES      | SCRIPTION                                           |    |

|--------------------|-----------------------------------------------------|----|

| 2 FEATURES         |                                                     | 1  |

|                    | FOR 92 SERIES PRODUCTS                              |    |

| ORDERING INFO      | DRMATION                                            | 5  |

|                    |                                                     |    |

| 3 PIN DESCRIPT     | TON                                                 | 10 |

|                    | onfiguration                                        |    |

|                    | Pin Definition                                      |    |

|                    | guration                                            |    |

|                    | Definition                                          |    |

| 3.3 28 Pin Confi   | guration                                            | 23 |

| 3.3.1 28 Pin       | Definition                                          | 24 |

| 4 INNER BLOCK      | DIAGRAM                                             | 28 |

|                    | AND SRAM                                            |    |

|                    | LDROM                                               |    |

|                    | ndependent EEPROM                                   |    |

|                    | QUE ID AREA                                         |    |

|                    | e ID Read Operating Demo Program In C Language      |    |

|                    | 1                                                   |    |

| 5.5 programing     |                                                     | 32 |

| 5.6 In Application | on Programming (IAP)                                | 33 |

| 5.6.1 IAP Op       | peration Related Registers                          | 34 |

|                    | perating Process                                    |    |

|                    | perating Notesperating Demo Program In C Language   |    |

| ·                  |                                                     |    |

|                    | pader Mode operation related registers              |    |

|                    |                                                     |    |

|                    | ption Area (User Programming Settings)              |    |

|                    | mer-Option-related Registers Operation Instructions |    |

|                    |                                                     |    |

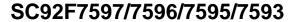

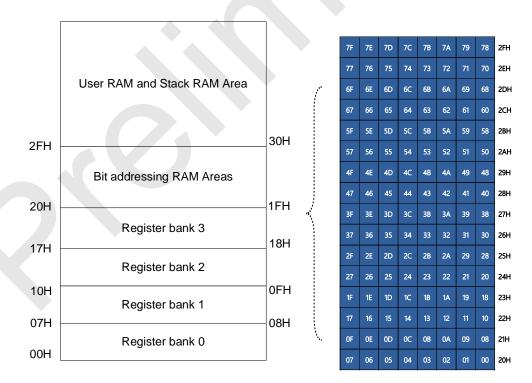

| 5.10.1 Interr      | nal 256 bytes SRAM                                  | 55 |

| 5.10.2 Exter       | nal 1792 bytes SRAM                                 | 56 |

|                    | CTION REGISTER (SFR)                                |    |

|                    | g                                                   |    |

|                    |                                                     |    |

| o.∠ SFK INSTRUC    | tions                                               | 5  |

# Super High-Speed 1T 8051 Core Flash MCU

| 6.2.1 PWM Duty Cycle Adjustment Register              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2.2 LCD/LED Display RAM Configuration               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7 POWER, RESET AND SYSTEM CLOCK                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.1 Power Circuit                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.2 Power-on Reset                                    | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

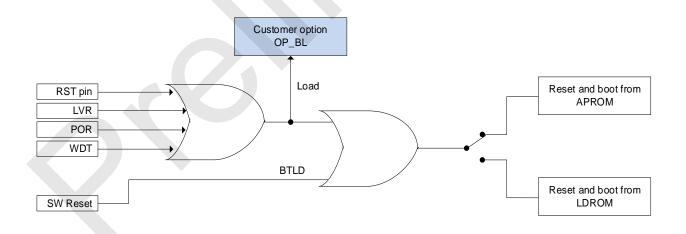

| 7.2.1 Reset Stage                                     | A contract of the contract of |

| 7.2.2 Loading Information Stage                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

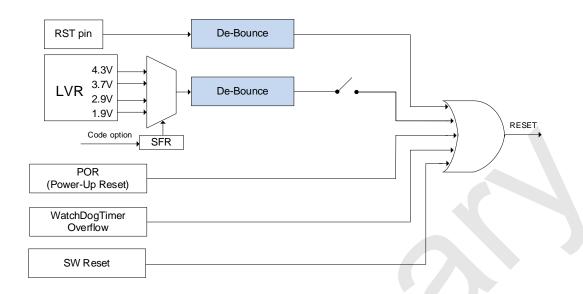

| 7.3 Reset Modes                                       | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.3.1 External Reset                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.3.2 Low-voltage Reset LVR                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.3.3 Power-on Reset (POR)7.3.4 Watchdog Reset (WDT)  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.3.5 Software Reset                                  | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.3.6 Register Reset Value                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.4 High-speed RC Oscillator                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.5 Low-speed RC Oscillator and Low-speed Clock Timer |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.6 Power Saving Modes                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8 CPU AND INSTRUCTION SET                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.1 CPU                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.2 Addressing Mode                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.2.1 Immediate Addressing                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.2.2 Direct Addressing                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.2.4 Register Addressing                             | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.2.5 Relative Addressing<br>8.2.6 Indexed Addressing |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.2.7 Bits Addressing                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9 INTERRUPTS                                          | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.1 Interrupt Source and Vector                       | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.2 Interrupt Structure Diagram                       | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.3 Interrupt Priority                                | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.4 Interrupt Processing Flow                         | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.5 Interrupt-related SFR Registers                   | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

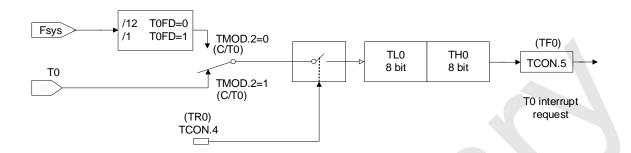

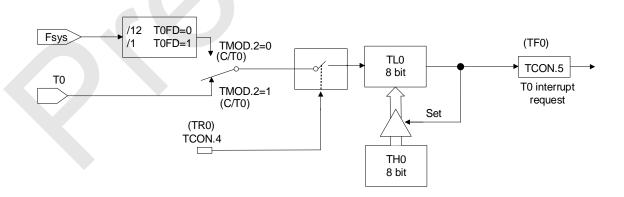

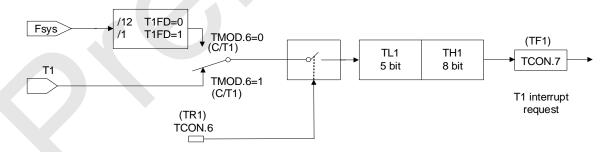

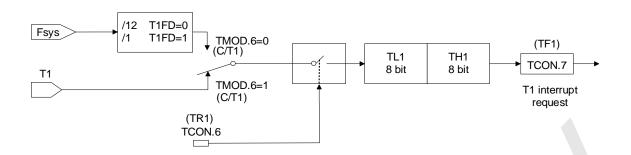

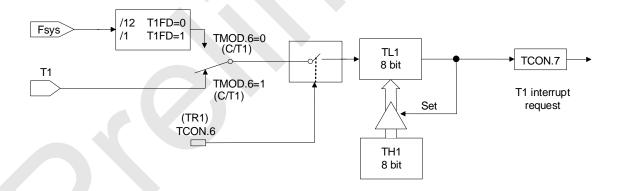

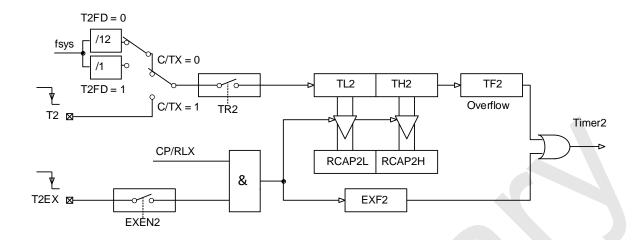

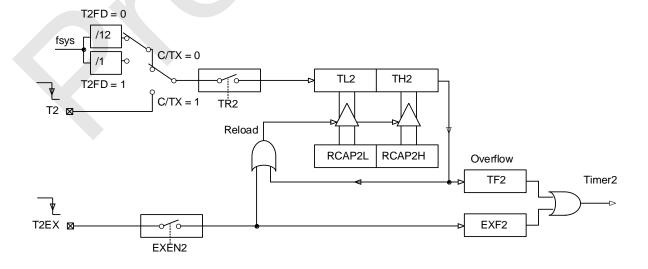

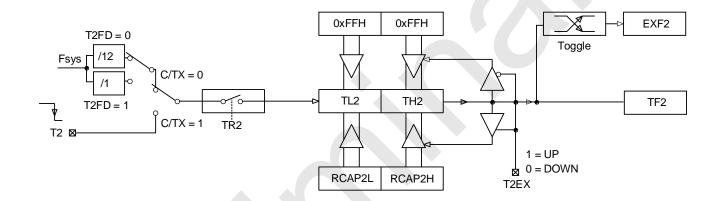

| 10 TIMER/COUNTER T0 AND T1                            | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

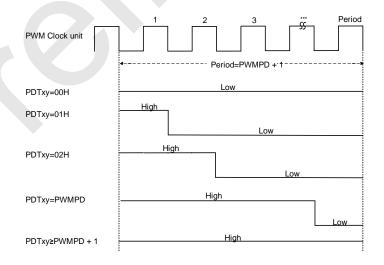

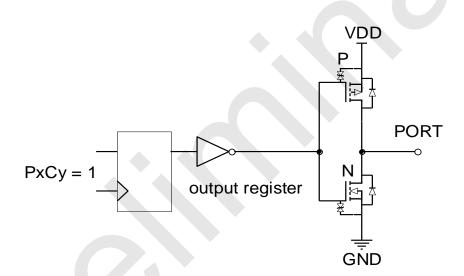

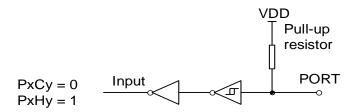

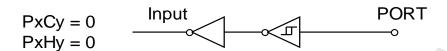

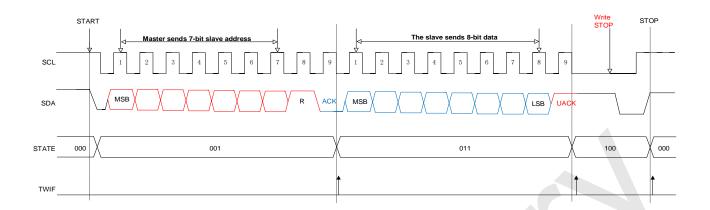

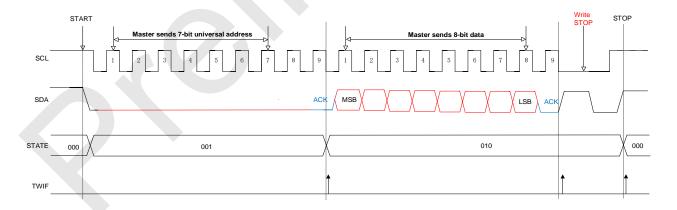

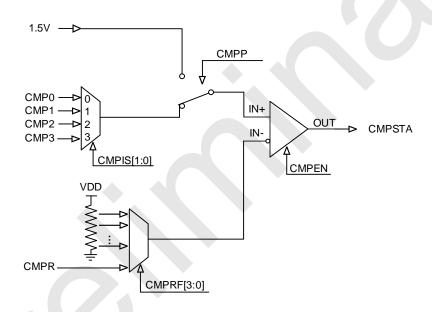

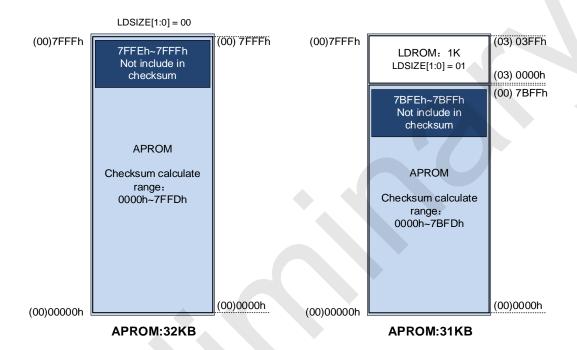

| 10.1 T0 and T1-related Registers                      | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |