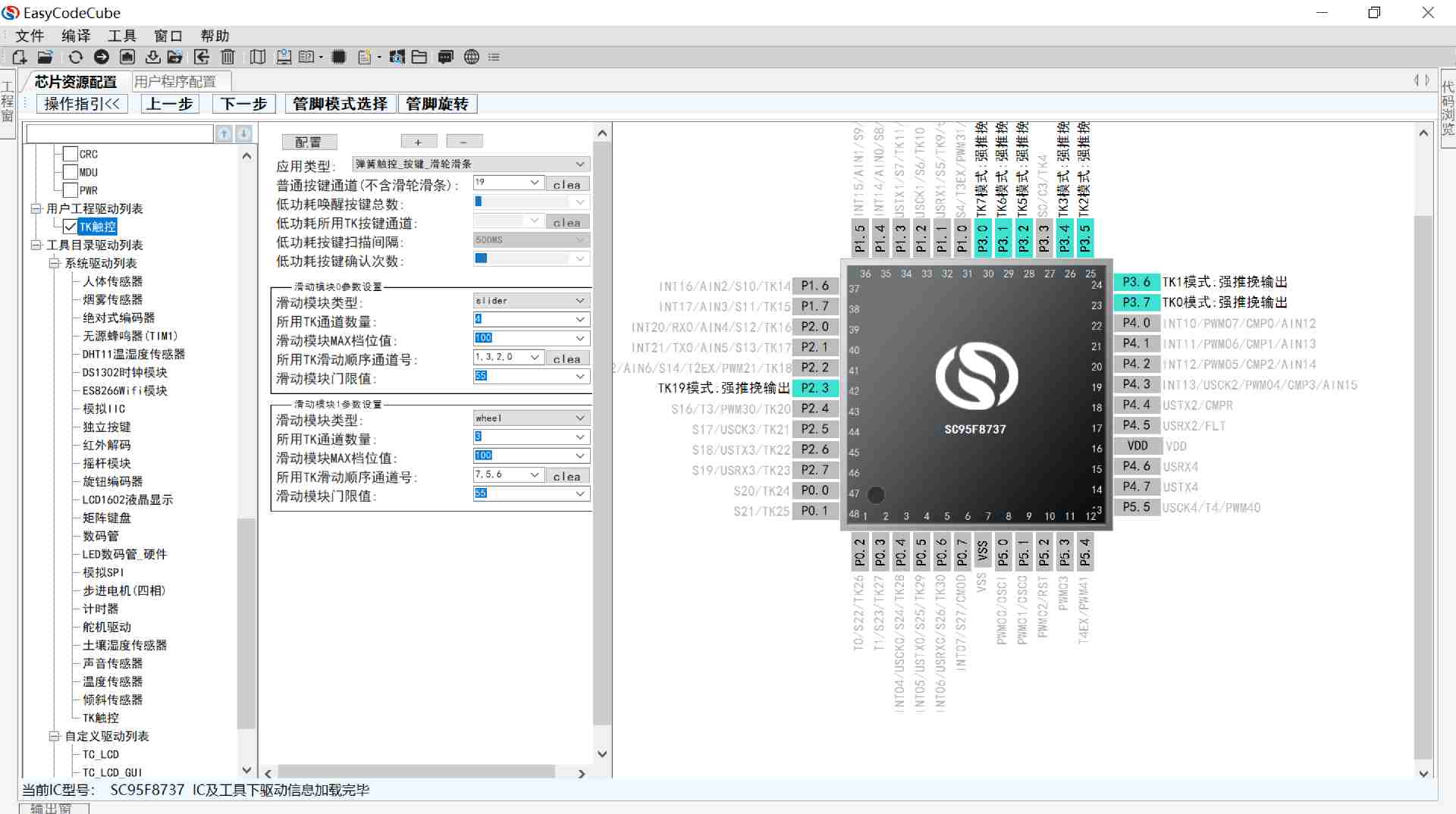

SC LINK PRO is designed for offline/online programming & simulation and TouchKey debugging of SC92F/93F/95F series MCU

Products

SC92F7302

Operating Voltage: 2.4V ~ 5.5V

Operating Temperature: -40 ~ 85℃

EMS

l ESD

n HBM:MIL-STD-883J Class 3B

n MM:JEDEC EIA/JESD22-A115 Class C

n CDM:ANSI/ESDA/JEDEC JS-002-2018 Class C3

l EFT

n EN61000-4-4 Level 4

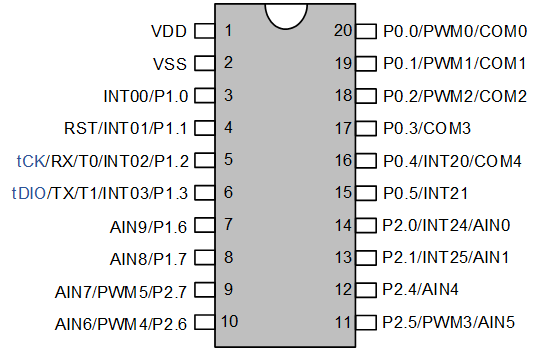

Package:

SOP20/TSSOP20/QFN20

Core: High speed 1T 8051

Flash ROM: 8K bytes Flash ROM (MOVC) prohibited addressing 0000H ~ 00FFH) can be rewritten for 10, 000 times

IAP:

l Can be Code option into 0K, 0.5K, 1K or 8K

l When the user performs IAP operations on the Flash ROM, the LVR should be set to 3.7V or higher, and the VDD voltage should be set between 3.7V and 5.5V

l When the user performs IAP operations on the EEPROM, the VDD voltage should be set between 2.4V and 5.5V

Attention: The programming voltage can only be 5V, when the chip is being programmed by users!

EEPROM: Independent 128 bytes, EEPROM can be rewritten for 100, 000 times. The data written-in has more than 10-year preservation life.

SRAM: Internal 256 bytes + external 256 bytes

System Clock (fSYS):

l Built-in high-frequency 24MHz oscillator (fHRC):

n The system clock source of IC can be set to one of the four types of frequency division by programmer selection:24MHz@3.7~5.5V, 12/6/2MHz@2.4~5.5V

n Frequency Error: no more than ±1% of frequency error in 2.4V ~ 5.5V and -40 ~ 85℃ application environment

Built-in Low-Frequency 32kHz Oscillator (LRC):

l Clock source of Base Timer (BTM), which can wake up the SC92F730X from stop mode

l Clock source of Watchdog (WDT)

Low-voltage Reset (LVR):

l 4-level LVR voltage options: 4.3V, 3.7V, 2.9V, 2.3V

l The default is the Code Option value selected by the user

Flash Programming and Emulation:

l 2-wire JTAG programming and emulation interface

Interruption (INT):

l 9 interrupt sources: Timer0, Timer1, Timer2, INT0, INT2, ADC, PWM, UART, Base Timer

l 2 external interrupt vectors shared by 8 interrupt ports, all of which can be defined in rising-edge, falling-edge or dual-edge trigger mode

l Two-level interrupt priority capability

Digital Peripheral:

l Up to 18 bidirectional independently controllable I/O interfaces, able to configure pull-high resistor independently

l P0/P2 ports with 4-level drive capability

l All I/Os equipped with sink current drive capability (70 mA)

l 11-bit WDT with optional clock division ratio

l 3 standard 80C51 Timer/Counters: Timer0, Timer1 and Timer2

l 6-channel 8-bit PWM output channels with variable period and individual duty cycle

l 5 I/Os as output of the 1/2-bias LCD COM

l 1 independent UART communication interface

Analog Peripheral:

l 9-channel 12-bit ADC

n Built-in 2.4V reference voltage

n 2 options for ADC reference voltage: VDD and internal 2.4V

n Internal one-channel ADC, where VDD can be measured directly

n ADC conversion completion interrupt

Power Saving Mode:

l IDLE Mode: can be woken up by any interrupt.

l STOP Mode: can be woken up by INT0, INT2、Base Timer