SC LINK PRO is designed for offline/online programming & simulation and TouchKey debugging of SC92F/93F/95F series MCU

Products

SC32F12TC9QJR

Operating Conditions

l Operating voltage: 2.0V~5.5V

l Operating temperature: -40 ~ +105℃

EMS

l ESD

n HBM:JEDECEIA/JESD22-A114F Class 3A

n MM:JEDEC EIA/JESD22-A115C Class C

n CDM:ANSI/ESDA/JEDEC JS-002-2022 Class C3

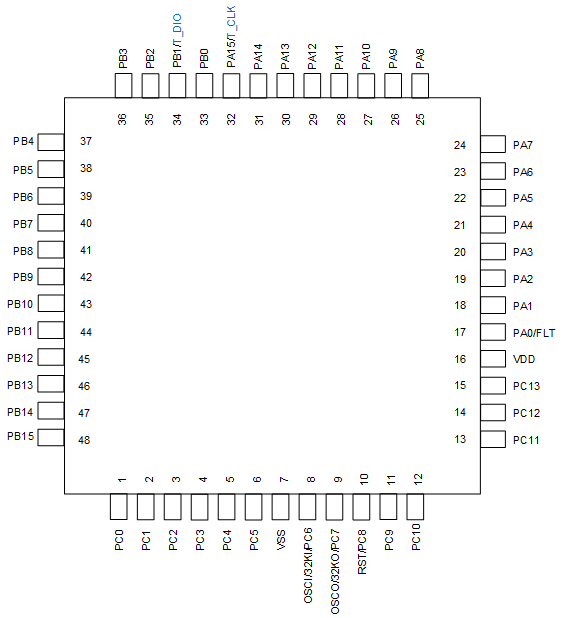

Package

l 48 PIN: QFN48 (5X5)

Core

l With Wakeup Interrupt Controller (WIC) module

l With MPU module

l 64-bits instruction prefetch

l Built-in Multiplier Unit (MDU)

Reset

l Power-On Reset (POR)

l Software Reset

l Reset through external NRST pin (PC8) with a low-level signal

l Watchdog Timer (WDT) reset

l Low Voltage Reset (LVR)

n Four selectable reset voltages: 4.3V, 3.7V, 2.9V, 1.9V

n The default value is determined by the user's programmed Code Option

BUS

l 1 IOPORT

l 1 AHB

l 3 APB:APB0~APB2

Power Saving Mode

l Low-Speed Mode, system clock source can be selected as LIRC, and CPU can work at 32MHz

l IDLE Mode, can be woken up by any interrupt

l STOP Mode, can be woken up by INT0~15, Base Timer, TK, and CMP

APROM

l Up to 512 Kbytes APROM

l Can be rewritten up to 100,000 times

l Supports hardware read protection encryption

l Supports hardware write protection: Provides two regions for disabling IAP (In-Application Programming) operations. Users can configure the settings through the Code Option, with the minimum setting unit being 512 bytes (one sector)

LDROM

l 4 Kbytes of system storage area, factory-programmed with BootLoader program

SRAM

l 16 Kbytes Internal SRAM

l Supports parity check:

n An additional 2K RAM is used for parity checking, which means SRAM data bus width is 36 bits, with 4 bits dedicated to parity check (one bit per byte).

n The parity check bits are calculated and saved when writing to the SRAM, and automatically verified upon reading. If a bit fails, an unmaskable interrupt (Cortex®-M0+ NMI) will be generated.

n Provides an independent SRAM parity error flag, SRAMPEIF.

n Pay attention to the initialization of the SRAM when in use.

l Supports booting from SRAM

1.5K Bytes User Storage Aera(generic EEPROM)

l Divided into three 512 bytes sectors

l Can be rewritten up to 100,000 times

l Data retention time is over 100 years at room temperature

96 bits unique ID

l 96-bit Unique ID defined in the design option area

l Hardware method: System storage area of 4 Kbytes, factory-programmed with BootLoader program

l Software method: Supports interrupt vector table remapping, allowing flexible partitioning of the APROM area for user BootLoader program execution

1.3 Flash Programming and Emulation

l Programming methods supported: ICP / ISP / IAP

l 2-wire JTAG / SWD programming and emulation interface

l Simulation functionality is not supported in encrypted mode

Built-in high-frequency 64 MHz oscillator (HIRC)

l Can be selected as the system clock source

l The default clock frequency when power on ”fSYS” is fHIRC/2

l Frequency Error: Within ±1% @ -40 ~ 105℃ @ 2.0V~ 5.5V

l The system clock can be automatically calibrated by 32.768 kHz external crystal oscillator, after calibration HIRC accuracy can be infinitely close to the accuracy of external 32.768 kHz crystal oscillator

Built-in low-frequency 32 kHz oscillator (LIRC)

l Can be selected as the system clock source

l Fixed as the WDT clock source, which will be automaticlly enabled when WDT is enabled

l Can be selected as the Base Timer clock source

l Can be selected as the LCD/LED clock source

l Frequency Error: Within ±4% @ -20 ~ 85℃ @ 4.0V~ 5.5V, after register correction

External 2~16MHz crystal oscillator (HXT)

l Can be selected as the system clock source

l User can choose an external crystal oscillator oscillating frequency of <12MHz or ≥12MHz

External 32.768 KHz crystal oscillator (LXT)

l Can be selected as the system clock source

l Can be selected as the Base Timer clock source

l Can be selected as the LCD/LED clock source

l Allows for an external 32.768kHz oscillator

l Automatic calibration of HIRC can be performed using LXT

l Up to 25 interrupts

l Four-level interrupt priority can be set

n 16 interrupts, occupying 4 interrupt vectors in total

n Change Interrupts on All GPIO pins

n All interrupts can be set as rising edge, falling edge, or both-edge interrupts, each with an independent corresponding interrupt flag

n Setting the corresponding interrupt flag in software triggers entry into the corresponding interrupt

Up to 46 GPIOs

l Independent pull-up resistor configuration is available

l All GPIO pins have source driving capability controlled by four levels

l All GPIO pins have high sink current driving capability (50mA)

Watchdog timer (WDT)

l Built-in WDT with programmable overflow time ranging from 3.94ms to 500ms

Base Timer(BTM)

l The clock sources LXT and LIRC are selectable

l Selectable interrupt frequency intervals from 15.625ms to 32s

l Can wake up from STOP Mode

8 16-bit timers: Timer0~Timer7

l 16-bit up, down, and up/down auto-reload counters

l Supports rising edge/falling edge capture for PWM duty and period capture

l Each TIM can provide two channels of synchronized and adjustable duty cycle PWM outputs (TPWMA/TPWMB).

l TIM1/2/6 timer overflow and capture events can trigger DMA requests

8 channels 16-bit Advanced PWM0

l The clock source can be selected up to 64MHz

l Shared period and independently adjustable duty cycle

l Support dead time and complementary PWM output

l Support center-aligned mode

l Support fault detection

32 channels 8-bit LEDPWM

l Shared period and independently adjustable duty cycle

l Support center-aligned mode

6 independent UART: UART0~5

l UART2 has a full LIN interface, offering the following capabilities:

n Master and slave mode switching

n Hardware break transmission in master mode(10/13bits)

n Hardware break detection in slave mode(10/11bits)

n Baud rate synchronization in slave mode

n Provision of related interrupts, status bits, and flags

l Each UART ports can be mapped to 2 sets of IO pins

l Independent baud rate generator

l UART2 does not support wake-up from STOP Mode

l UART0/1/3/4/5 support wake-up from STOP Mode

l Three communication modes available

n Mode 0: 8-bit half-duplex synchronous communication

n Mode 1: 10-bit full-duplex asynchronous communication

n Mode 3: 11-bit full-duplex asynchronous communication

l UART0 and UART1 support DMA requests

l UART2~5 do not support DMA requests

3 independent SPI: SPI0~2

l SPI0:

n A 16-bit 8-level FIFO with separate transmit and receive

n In SPI mode, the drive capability of the corresponding signal pins will be enhanced

n Can be mapped to 4 sets of ports

n Supports DMA

l SPI1:

n Can be mapped to 4 set of ports

n Supports DMA

l SPI2:

n Can be mapped to 4 set of ports

n Do not support DMA

2 independent TWI: TWI0/TWI1

l Supports master mode or slave mode

l Supports clock stretching in slave mode

l Communication speed of up to 1Mbps

l TWI0 supports DMA

l TWI0 signal ports can be mapped to 6 set of ports

l TWI1 signal ports can be mapped to 6 set of ports

CRC

l Initial value can be set, with a default of 0xFFFF_FFFF

l Polynomial can be programmed, with a default of 0x04C1_1DB7

l Supports 8/16/32-bit data units

LCD/LED Driver

l The clock sources LXT and LIRC are selectable

l LCD and LED are mutually exclusive options, sharing registers and ports

l LED:

n Supports 8 X 24, 6 X 26, 5 X 27, or 4 X 28 segment LED driving

n LED segment port has source driving capability controlled by four levels

n Shares registers with 32-channel LEDPWM, allowing LED replacement driving and grayscale adjustment through center-aligned PWM waveforms

l LCD:

n Supports 8 X 24, 6 X 26, 5 X 27, or 4 X 28 segment LCD driving

n LCD voltage output port has selectable voltage divider resistor values

n Two bias voltages options: 1/3 and 1/4

n Two waveform modes: Type A and Type B

n Three frame frequencies available:

u 32/64/128 Hz in Type A mode

u 64/128/256 Hz in Type B mode

DMA

l 2 independent configurable channels

l Each DMA channel can send DMA requests to other channels

l Data width supports byte, half-word, and word

l 22 DMA request sources with four priority levels

l Supports source/destination address auto-increment or fixed

l Supports single and burst transfer modes

l Transfer modes: memory to memory, memory to peripheral, peripheral to memory, peripheral to peripheral

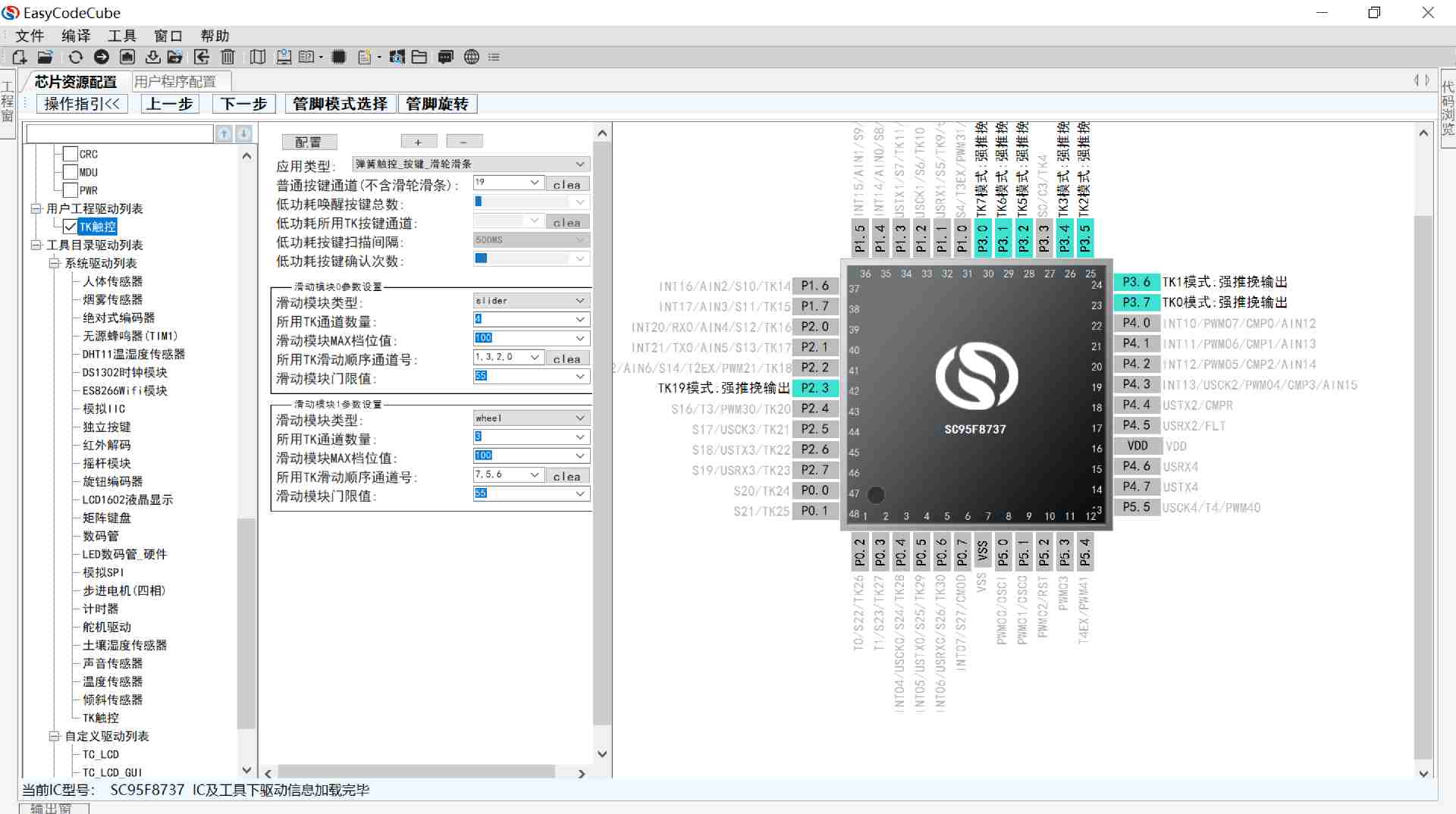

37-channel high-sensitivity Touch Key circuit

l Exclusive to the SC32F12T series

l Channels can be scanned in parallel

l CMOD capacitor can only be externally connected

l Supports self-capacitance mode and mutual-capacitance mode

l Supports low-power mode

l Supports fast wake-up STOP mode

l Suitable for touch applications with high sensitivity requirements, such as proximity sensing and touch keys

l Comprehensive development support: Highly flexible touch software library, intelligent debugging software

Analog-to-Digital Converter ADC

l Precison: 14 bits

l Supports up to 18 channels

n External 16 ADC sampling channels can be multiplexed with I/O ports for other functions

n One internal ADC can directly measure VDD voltage

n One internal ADC can directly measure OP output

l Four options for ADC reference voltage: VDD, and internal 2.048V, 1.024V, or 2.4V

l Configurable ADC conversion completion interrupt

l Supports single-channel continuous conversion mode

l Supports DMA transmission: DMA request will be generated after ADC conversion complete

l The conversion results feature an overflow flag: OVERRUN, and the OVERRUN flag bit is located in the same register as the ADC conversion results so users can read the information all at once.

Operational Amplifier(OP)

l A rail-to-rail input stage

l Can be configurable as a Programmable Gain Amplifier (PGA)

n Non-inverting gain: 8/16/32/64

n Inverting gain: 7/15/31/63

l Two external pins for the non-inverting input: OP_P0 or OP_P1

l One external pin for the inverting input: OP_N

l One external pin for the output: OP_O

l The output can be directly connected to the ADC input

l The output can be directly connected to the positive input of a Comparator (CMP)

Analog Comparator CMP

l Five positive input signal selectable:

n Four analog signal positive input terminals: CMP0~CMP3

n OP output signal

l Negative input voltage can be selected from CMPR input or one of the 15 comparison voltages derived from the internal VDD voltage division

l CMP interrupts can wake up the STOP mode